- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄379081 > CY7C1514AV18-167BZC (CYPRESS SEMICONDUCTOR CORP) 72-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1514AV18-167BZC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類(lèi): | DRAM |

| 英文描述: | 72-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| 中文描述: | 2M X 36 QDR SRAM, 0.5 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1.40 MM HEIGHT, MO-216, FBGA-165 |

| 文件頁(yè)數(shù): | 22/26頁(yè) |

| 文件大小: | 1074K |

| 代理商: | CY7C1514AV18-167BZC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

PRELIMINARY

CY7C1510AV18

CY7C1525AV18

CY7C1512AV18

CY7C1514AV18

Document #: 001-06984 Rev. *B

Page 22 of 26

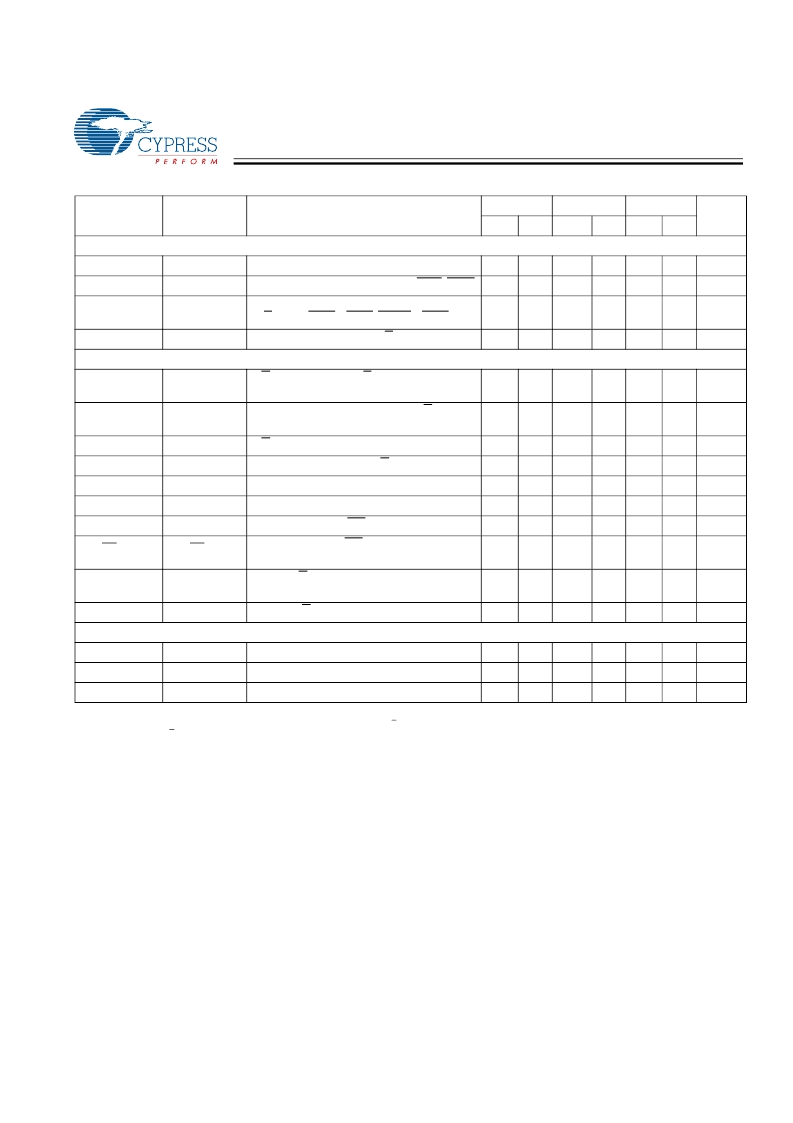

Hold Times

t

HA

t

HC

t

HCDDR

t

KHAX

t

KHIX

t

KHIX

Address Hold after K Clock Rise

Control Hold after K Clock Rise (RPS, WPS) 0.35

Double Data Rate Control Hold after Clock

(K/K) Rise (BWS

0

, BWS

1

, BWS

3

, BWS

4

)

D

[X:0]

Hold after Clock (K/K) Rise

0.35

–

–

–

0.4

0.4

0.4

–

–

–

0.5

0.5

0.5

–

–

–

ns

ns

ns

0.35

t

HD

Output Times

t

CO

t

KHDX

0.35

–

0.4

–

0.5

–

ns

t

CHQV

C/C Clock Rise (or K/K in Single Clock

Mode) to Data Valid

Data Output Hold after Output C/C Clock

Rise (Active to Active)

C/C Clock Rise to Echo Clock Valid

Echo Clock Hold after C/C Clock Rise

Echo Clock High to Data Valid

Echo Clock High to Data Invalid

Output Clock (CQ/CQ) HIGH

[26]

CQ Clock Rise to CQ Clock Rise

[26]

(rising edge to rising edge)

Clock (C/C) Rise to High-Z (Active to

High-Z)

[27, 28]

Clock (C/ C) Rise to Low-Z

[27, 28]

–

0.45

–

0.45

–

0.50

ns

t

DOH

t

CHQX

–0.45

–

-0.45

–

-0.50

–

ns

t

CCQO

t

CQOH

t

CQD

t

CQDOH

t

CQH

t

CQHCQH

t

CHCQV

t

CHCQX

t

CQHQV

t

CQHQX

t

CQHCQL

t

CQHCQH

–

0.45

–

0.30

–

–

–

–

0.45

–

0.35

–

–

–

–

0.50

–

0.40

–

–

–

ns

ns

ns

ns

ns

ns

–0.45

–

-0.30

1.55

1.55

-0.45

–

-0.35

1.95

1.95

-0.50

–

-0.40

2.45

2.45

t

CHZ

t

CHQZ

–

0.45

–

0.45

–

0.50

ns

t

CLZ

DLL Timing

t

KC Var

t

KC lock

t

KC Reset

Notes:

26.These parameters are extrapolated from the input timing parameters (t

- 250ps, where 250ps is the internal jitter. An input jitter of 200ps (t

KC Var

) ia already

included in the t

). These parameters are only guaranteed by design and are not tested in production.

27.t

, t

, are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads. Transition is measured

±

100 mV from steady-state voltage.

28.At any given voltage and temperature t

CHZ

is less than t

CLZ

and t

CHZ

less than t

CO

.

t

CHQX1

-0.45

–

-0.45

–

-0.50

–

ns

t

KC Var

t

KC lock

t

KC Reset

Clock Phase Jitter

DLL Lock Time (K, C)

K Static to DLL Reset

–

0.20

–

–

–

0.20

–

–

–

0.20

–

–

ns

1024

30

1024

30

1024

30

Cycles

ns

Switching Characteristics

Over the Operating Range

[22, 23]

Cypress

Parameter

Consortium

Parameter

Description

250 MHz

Min.

200 MHz

Min.

167 MHz

Min.

Unit

Max

Max

Max

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1514AV18-167BZI | 72-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| CY7C1514AV18-167BZXC | 72-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| CY7C1514AV18-167BZXI | 72-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| CY7C1514AV18-200BZC | 72-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| CY7C1514AV18-200BZI | 72-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1514AV18-167BZXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 2M x 36 1.8V QDR II 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1514AV18-200BZC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 2M x 36 1.8V QDR II 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1514AV18-200BZI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 2M x 36 1.8V QDR II 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1514AV18-200BZXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1514AV18-200BZXI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 2M x 36 1.8V QDR II 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。