- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379094 > CY7C43636 (Cypress Semiconductor Corp.) 512 x36/x18x2 Tri Bus FIFO(512 x36/x18x2 三路總線 先進先出) PDF資料下載

參數(shù)資料

| 型號: | CY7C43636 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 512 x36/x18x2 Tri Bus FIFO(512 x36/x18x2 三路總線 先進先出) |

| 中文描述: | 512 x36/x18x2三總線的FIFO(512 x36/x18x2三路總線先進先出) |

| 文件頁數(shù): | 13/40頁 |

| 文件大?。?/td> | 577K |

| 代理商: | CY7C43636 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

CY7C43626

CY7C43636/CY7C43646

CY7C43666/CY7C43686

13

PRELIMINARY

Notes:

17. CSA=LOW, W/RA=HIGH, MBA=LOW. It is not necessary to program offset register on consecutive clock cycles.

18. t

is the minimum time between the rising CLKA edge and a rising CLKB for FFC/IRC to transition HIGH in the next cycle. If the time between the rising

edge of CLKA and rising edge of CLKC is less than t

SKEW1

, then FFC/IRC may transition HIGH one cycle later than shown.

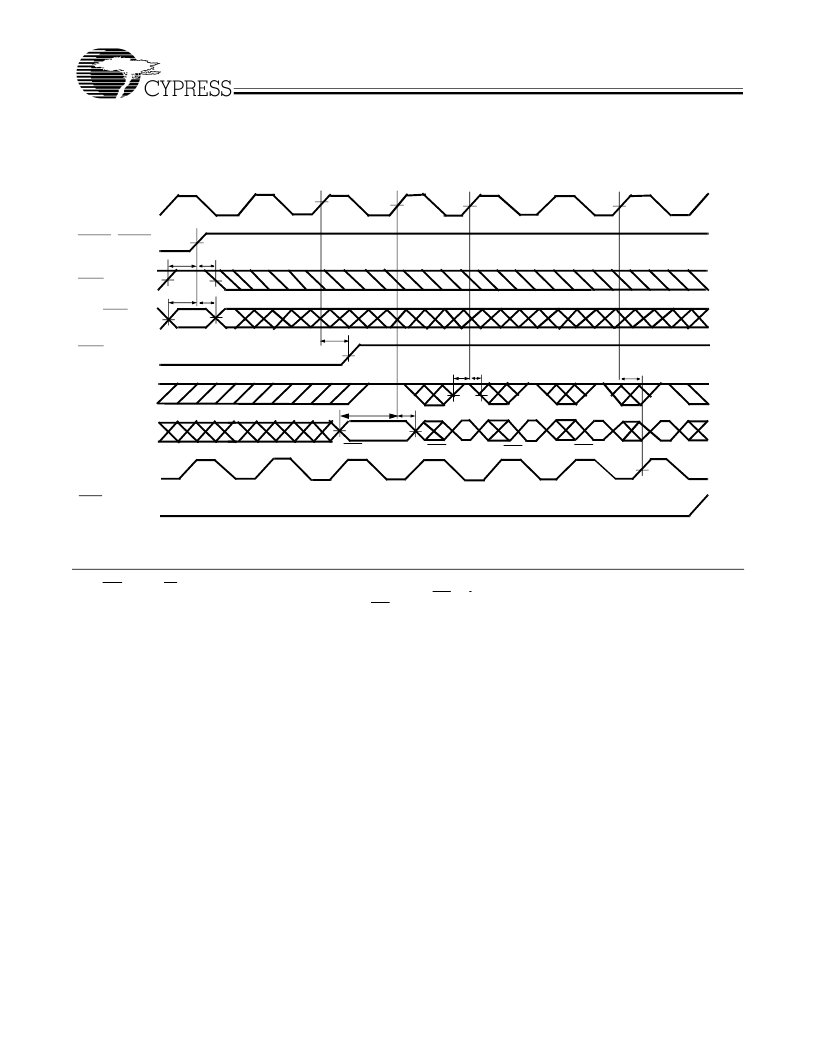

Switching Waveforms

(continued)

Parallel Programming of the Almost-Full Flag and Almost-Empty Flag Offset Values after Reset

(CY Standard and FWFT Modes)

t

WFF

t

FSS

t

DS

t

FSS

t

FSH

t

FSH

t

ENS

t

ENH

t

DH

t

SKEW1[18]

AFA Offset (Y1)

AFC Offset (Y2)

First Word to FIFO1

CLKA

MRS1, MRS2

SPM

FS1/SEN,

FS0/SD

FFA/IRA

ENA

A

0

35

CLKB

FFC/IRC

[17]

AEB Offset (X1)

AEA Offset (X2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C43626 | 256 x36/x18x2 Tri Bus FIFO(256 x36/x18x2 三路總線先進先出) |

| CY7C43646 | 1K x36/x18x2 Tri Bus FIFO(1K x36/x18x2 三路總線 先進先出) |

| CY7C43666 | 4K x36/x18x2 Tri Bus FIFO(4K x36/x18x2 三路總線先進先出) |

| CY7C43686 | 16K x36/x18x2 Tri Bus FIFO(16K x36/x18x2 三路總線先進先出) |

| CY7C43662AV | 3.3V 4K x36 x2 Bidirectional Synchronous FIFO(3.3V 4K x36 x2 雙向同步先進先出) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C43642-10AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Depth/Width Bi-Dir 1K x 36 x 2 120-Pin TQFP |

| CY7C43643-15AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Depth/Width Uni-Dir 1K x 36 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43643AV-10AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Depth/Width Uni-Dir 1K x 36 128-Pin TQFP |

| CY7C43643AV-15AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Depth/Width Uni-Dir 1K x 36 128-Pin TQFP |

| CY7C43643AV-7AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Depth/Width Uni-Dir 1K x 36 128-Pin TQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。