- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379096 > CY7C63310 (Cypress Semiconductor Corp.) enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C63310 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| 中文描述: | enCoRe II還低速USB外設(shè)控制器(enCoRe II還低速的USB外設(shè)控制器) |

| 文件頁數(shù): | 29/74頁 |

| 文件大小: | 1441K |

| 代理商: | CY7C63310 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

CY7C63310

CY7C638xx

Document 38-08035 Rev. *I

Page 29 of 74

13.0

Low-voltage Detect Control

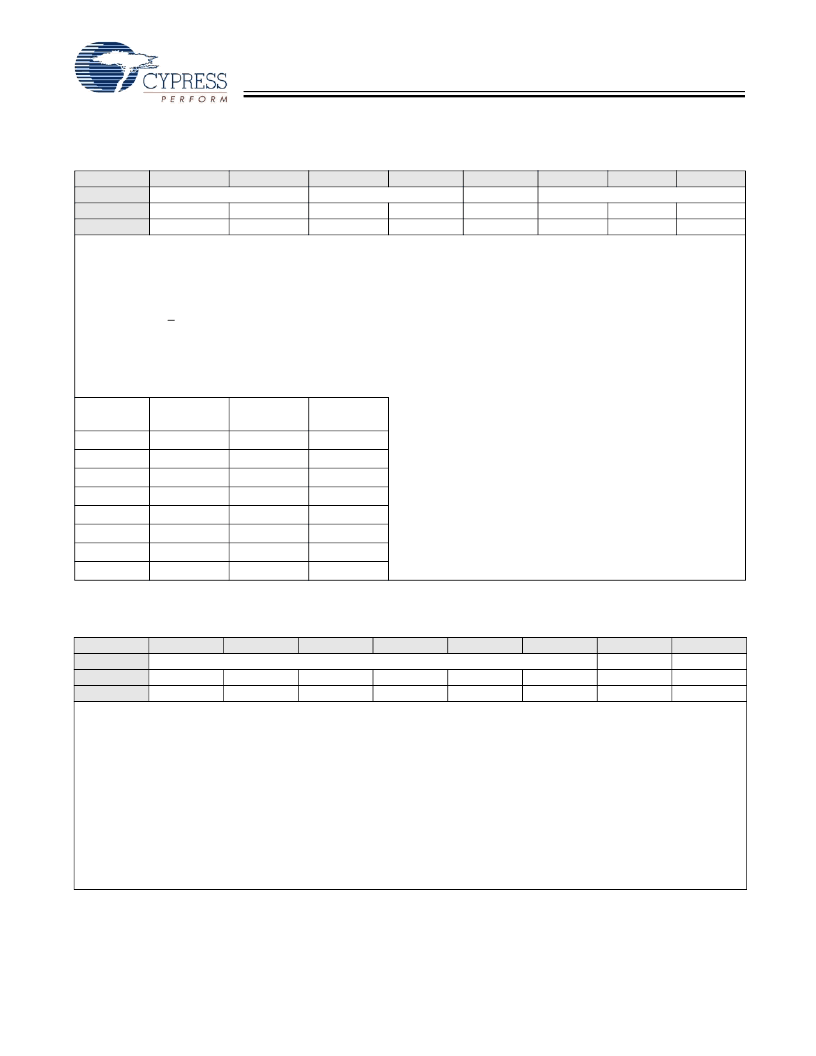

Table 13-1. Low-voltage Control Register (LVDCR) [0x1E3] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

PORLEV[1:0]

Reserved

VM[2:0]

Read/Write

–

–

R/W

R/W

–

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

This register controls the configuration of the Power-on Reset/Low-voltage Detection block

Bit [7:6]:

Reserved

Bit [5:4]:

PORLEV[1:0]

This field controls the level below which the precision power-on-reset (PPOR) detector generates a reset

0 0 = 2.7V Range (trip near 2.6V)

0 1 = 3V Range (trip near 2.9V)

1 0 = 5V Range, >4.75V (trip near 4.65V)

1 1 = PPOR will not generate a reset, but values read from the Voltage Monitor Comparators Register (

Table 13-2

) give the

internal PPOR comparator state with trip point set to the 3V range setting

Bit 3:

Reserved

Bit [2:0]:

VM[2:0]

This field controls the level below which the low-voltage-detect trips—possibly generating an interrupt and the level at which the

Flash is enabled for operation.

LVD Trip Point

(V) Min

Point (V) Typ

(V) Max

000

2.681

2.70

2.735

001

2.892

2.92

2.950

010

2.991

3.02

3.053

011

3.102

3.13

3.164

100

4.439

4.48

4.528

101

4.597

4.64

4.689

110

4.680

4.73

4.774

111

4.766

4.82

4.862

VM[2:0]

LVD Trip

LVD Trip Point

Table 13-2. Voltage Monitor Comparators Register (VLTCMP) [0x1E4] [R]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

LVD

PPOR

Read/Write

–

–

–

–

–

–

R

R

Default

0

0

0

0

0

0

0

0

This read-only register allows reading the current state of the Low-voltage-Detection and Precision-Power-On-Reset compar-

ators

Bit [7:2]:

Reserved

Bit 1:

LVD

This bit is set to indicate that the low-voltage-detect comparator has tripped, indicating that the supply voltage has gone below

the trip point set by VM[2:0] (See

Table 13-1

)

0 = No low-voltage-detect event

1 = A low-voltage-detect has tripped

Bit 0:

PPOR

This bit is set to indicate that the precision-power-on-reset comparator has tripped, indicating that the supply voltage is below

the trip point set by PORLEV[1:0]

0 = No precision-power-on-reset event

1 = A precision-power-on-reset event has occurred

Note:

This register can only be accessed in the second bank of I/O space. This requires setting the XIO bit in the CPU flags

register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C63801 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C63823 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C63813 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C63833 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C65640-LFXC | TetraHub High-speed USB Hub Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C63310-PXC | 功能描述:USB 接口集成電路 USB 3K Flash 128 byte RAM COM RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| CY7C63310-SXC | 功能描述:USB 接口集成電路 USB Peripheral Cntrl 3K/128 16-SOIC RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| CY7C63310-SXCES | 制造商:Cypress Semiconductor 功能描述: |

| CY7C634121C-PVXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C634121C-PXC | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。