- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379096 > CY7C63310 (Cypress Semiconductor Corp.) enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) PDF資料下載

參數(shù)資料

| 型號: | CY7C63310 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| 中文描述: | enCoRe II還低速USB外設(shè)控制器(enCoRe II還低速的USB外設(shè)控制器) |

| 文件頁數(shù): | 47/74頁 |

| 文件大小: | 1441K |

| 代理商: | CY7C63310 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當(dāng)前第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

CY7C63310

CY7C638xx

Document 38-08035 Rev. *I

Page 47 of 74

17.2

The sequence of events that occur during interrupt processing

is as follows:

1. An interrupt becomes active, either because:

a. The interrupt condition occurs (e.g., a timer expires)

b. A previously posted interrupt is enabled through an up-

date of an interrupt mask register

c. An interrupt is pending and GIE is set from 0 to 1 in the

CPU Flag register.

2. The current executing instruction finishes.

3. The internal interrupt is dispatched, taking 13 cycles. During

this time, the following actions occur: he MSB and LSB of

Program Counter and Flag registers (CPU_PC and

CPU_F) are stored onto the program stack by an automatic

CALL instruction (13 cycles) generated during the interrupt

acknowledge process.

a. The PCH, PCL, and Flag register (CPU_F) are stored

onto the program stack (in that order) by an automatic

CALL instruction (13 cycles) generated during the inter-

rupt acknowledge process

b. The CPU_F register is then cleared. Since this clears the

GIE bit to 0, additional interrupts are temporarily dis-

abled

c. The PCH (PC[15:8]) is cleared to zero

d. The interrupt vector is read from the interrupt controller

and its value placed into PCL (PC[7:0]). This sets the

program counter to point to the appropriate address in

the interrupt table (e.g., 0004h for the POR/LVD inter-

rupt)

4. Program execution vectors to the interrupt table. Typically,

a LJMP instruction in the interrupt table sends execution to

the user's Interrupt Service Routine (ISR) for this interrupt

5. The ISR executes. Note that interrupts are disabled since

GIE = 0. In the ISR, interrupts can be re-enabled if desired

by setting GIE = 1 (care must be taken to avoid stack

overflow).

6. The ISR ends with a RETI instruction which restores the

Program Counter and Flag registers (CPU_PC and

CPU_F). The restored Flag register re-enables interrupts,

since GIE = 1 again.

Interrupt Processing

7. Execution resumes at the next instruction, after the one that

occurred before the interrupt. However, if there are more

pending interrupts, the subsequent interrupts will be

processed before the next normal program instruction.

17.3

Trigger conditions for most interrupts in

Table 17-1.

have been

explained in the relevant sections. However, conditions under

which the USB Active (interrupt address 0030h) and PS2 Data

Low (interrupt address 004Ch) interrupts are triggered are

explained below.

1. USB Active Interrupt: Triggered when the D+/- lines are in

a non-idle state i.e., K-state or SE0 state

2. PS2 Data Low Interrupt: Triggered when SDATA becomes

low when the SDATA pad is in the input mode for at least

6-7 32 KHz cycles.

Interrupt Trigger Conditions

17.4

The time between the assertion of an enabled interrupt and the

start of its ISR can be calculated from the following equation.

Latency = Time for current instruction to finish + Time for

internal interrupt routine to execute + Time for LJMP

instruction in interrupt table to execute.

For example, if the 5-cycle JMP instruction is executing when

an interrupt becomes active, the total number of CPU clock

cycles before the ISR begins would be as follows:

(1 to 5 cycles for JMP to finish) + (13 cycles for interrupt

routine) + (7 cycles for LJMP) = 21 to 25 cycles.

In the example above, at 24 MHz, 25 clock cycles take 1.042

μ

s.

Interrupt Latency

17.5

The Interrupt Clear Registers (INT_CLRx) are used to enable

the individual interrupt sources’ ability to clear posted inter-

rupts.

When an INT_CLRx register is read, any bits that are set

indicates an interrupt has been posted for that hardware

resource. Therefore, reading these registers gives the user the

ability to determine all posted interrupts.

Interrupt Registers

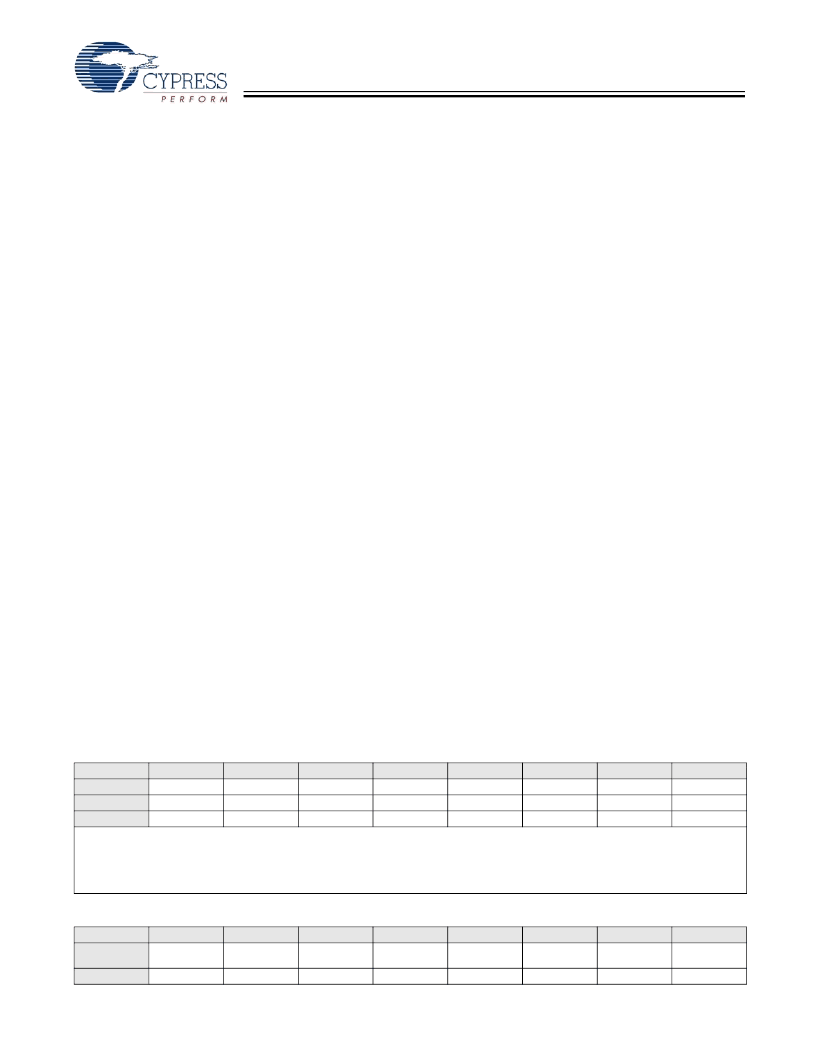

Table 17-2. Interrupt Clear 0 (INT_CLR0) [0xDA] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

GPIO Port 1

Sleep Timer

INT1

GPIO Port 0

SPI Receive

SPI Transmit

INT0

POR/LVD

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

When reading this register,

0 = There’s no posted interrupt for the corresponding hardware

1 = Posted interrupt for the corresponding hardware present

Writing a ‘0’ to the bits will clear the posted interrupts for the corresponding hardware. Writing a ‘1’ to the bits AND to the ENSWINT

(Bit 7 of the INT_MSK3 Register) will post the corresponding hardware interrupt

Table 17-3. Interrupt Clear 1 (INT_CLR1) [0xDB] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

TCAP0

Prog Interval

Timer

1-ms Timer

USB Active

USB Reset

USB EP2

USB EP1

USB EP0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C63801 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C63823 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C63813 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C63833 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C65640-LFXC | TetraHub High-speed USB Hub Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C63310-PXC | 功能描述:USB 接口集成電路 USB 3K Flash 128 byte RAM COM RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| CY7C63310-SXC | 功能描述:USB 接口集成電路 USB Peripheral Cntrl 3K/128 16-SOIC RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| CY7C63310-SXCES | 制造商:Cypress Semiconductor 功能描述: |

| CY7C634121C-PVXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C634121C-PXC | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。