- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379096 > CY7C63823 (Cypress Semiconductor Corp.) enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C63823 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| 中文描述: | enCoRe II還低速USB外設(shè)控制器(enCoRe II還低速的USB外設(shè)控制器) |

| 文件頁(yè)數(shù): | 33/74頁(yè) |

| 文件大小: | 1441K |

| 代理商: | CY7C63823 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)

CY7C63310

CY7C638xx

Document 38-08035 Rev. *I

Page 33 of 74

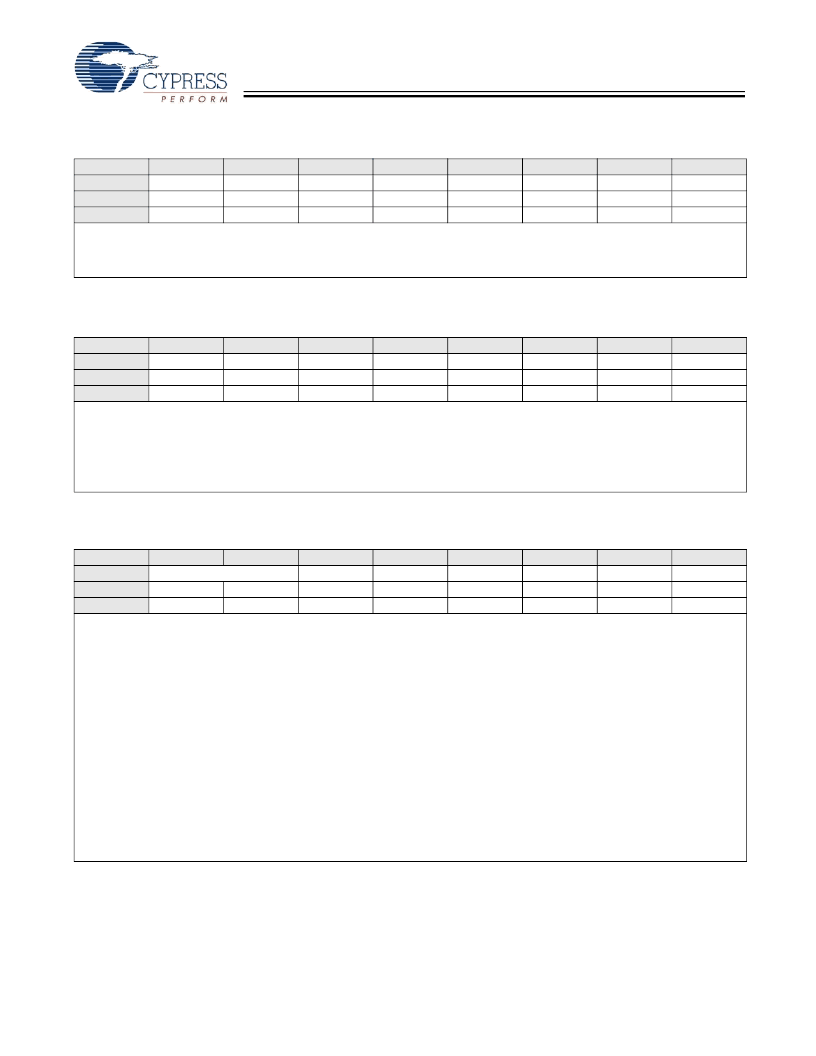

Table 14-5. P0.0/CLKIN Configuration (P00CR) [0x05] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

Int Enable

Int Act Low

TTL Thresh

High Sink

Open Drain

Pull-up Enable

Output Enable

Read/Write

--

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

This pin is shared between the P0.0 GPIO use and the CLKIN pin for an external clock. When the external clock input is enabled

the settings of this register are ignored

The use of the pin as the P0.0 GPIO is available in all the enCoRe II parts.

In the CY7C638xx, only 8 mA sink drive capability is available on this pin regardless of the setting of the High Sink bit

Table 14-6. P0.1/CLKOUT Configuration (P01CR) [0x06] R/W]

Bit #

7

6

5

4

3

2

1

0

Field

CLK Output

Int Enable

Int Act Low

TTL Thresh

High Sink

Open Drain

Pull-up Enable

Output Enable

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

This pin is shared between the P0.1 GPIO use and the CLKOUT pin. When CLK output is set, the internally selected clock is

sent out onto P0.1CLKOUT pin.

The use of the pin as the P0.1 GPIO is available in all the enCoRe II parts. In the CY7C638xx, only 8 mA sink drive capability

is available on this pin regardless of the setting of the High Sink bit

Bit 7:

CLK Output

0 = The clock output is disabled

1 = The clock selected by the CLK Select field (Bit [1:0] of the CLKIOCR Register—

Table 10-7

) is driven out to the pin

Table 14-7. P0.2/INT0–P0.4/INT2 Configuration (P02CR–P04CR) [0x07–0x09] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

Int Act Low

TTL Thresh

Reserved

Open Drain

Pull-up Enable

Output Enable

Read/Write

–

–

R/W

R/W

–

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

These registers control the operation of pins P0.2–P0.4 respectively. These pins are shared between the P0.2–P0.4 GPIOs and

the INT0–INT2. These registers exist in all enCoRe II parts. The INT0–INT2 interrupts are different than all the other GPIO

interrupts. These pins are connected directly to the interrupt controller to provide three edge-sensitive interrupts with independent

interrupt vectors. These interrupts occur on a rising edge when Int act Low is clear and on a falling edge when Int act Low is set.

These pins are enabled as interrupt sources in the interrupt controller registers (

Table 17-8

and

Table 17-6

).

To use these pins as interrupt inputs configure them as inputs by clearing the corresponding Output Enable. If the INT0–INT2

pins are configured as outputs with interrupts enabled, firmware can generate an interrupt by writing the appropriate value to the

P0.2, P0.3 and P0.4 data bits in the P0 Data Register

Regardless of whether the pins are used as Interrupt or GPIO pins the Int Enable, Int act Low, TTL Threshold, Open Drain, and

Pull-up Enable bits control the behavior of the pin

The P0.2/INT0–P0.4/INT2 pins are individually configured with the P02CR (0x07), P03CR (0x08), and P04CR (0x09) respec-

tively.

Note:

Changing the state of the Int Act Low bit can cause an unintentional interrupt to be generated. When configuring these

interrupt sources, it is best to follow the following procedure:

1. Disable interrupt source

2. Configure interrupt source

3. Clear any pending interrupts from the source

4. Enable interrupt source

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C63813 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C63833 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| CY7C65640-LFXC | TetraHub High-speed USB Hub Controller |

| CY7C65640 | TetraHub High-speed USB Hub Controller |

| CY7C65640-LFC | TetraHub High-speed USB Hub Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C63823-3XWC | 制造商:Cypress Semiconductor 功能描述:USB - Bulk 制造商:Cypress Semiconductor 功能描述:Bulk / USB Low-Speed Peripherals |

| CY7C638234-SXC | 功能描述:IC USB CONTROLLERS RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| CY7C638235-SXC | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cypress Semiconductor 功能描述: |

| CY7C63823-PXC | 功能描述:IC USB PERIPHERAL CTRLR 24-DIP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:CY7C 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| CY7C63823-QXC | 功能描述:USB 接口集成電路 USB Peripheral Cntrl 8K/256 24-QSOP RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。