- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379096 > CY7C63833 (Cypress Semiconductor Corp.) enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) PDF資料下載

參數(shù)資料

| 型號: | CY7C63833 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設(shè)控制器) |

| 中文描述: | enCoRe II還低速USB外設(shè)控制器(enCoRe II還低速的USB外設(shè)控制器) |

| 文件頁數(shù): | 40/74頁 |

| 文件大?。?/td> | 1441K |

| 代理商: | CY7C63833 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

CY7C63310

CY7C638xx

Document 38-08035 Rev. *I

Page 40 of 74

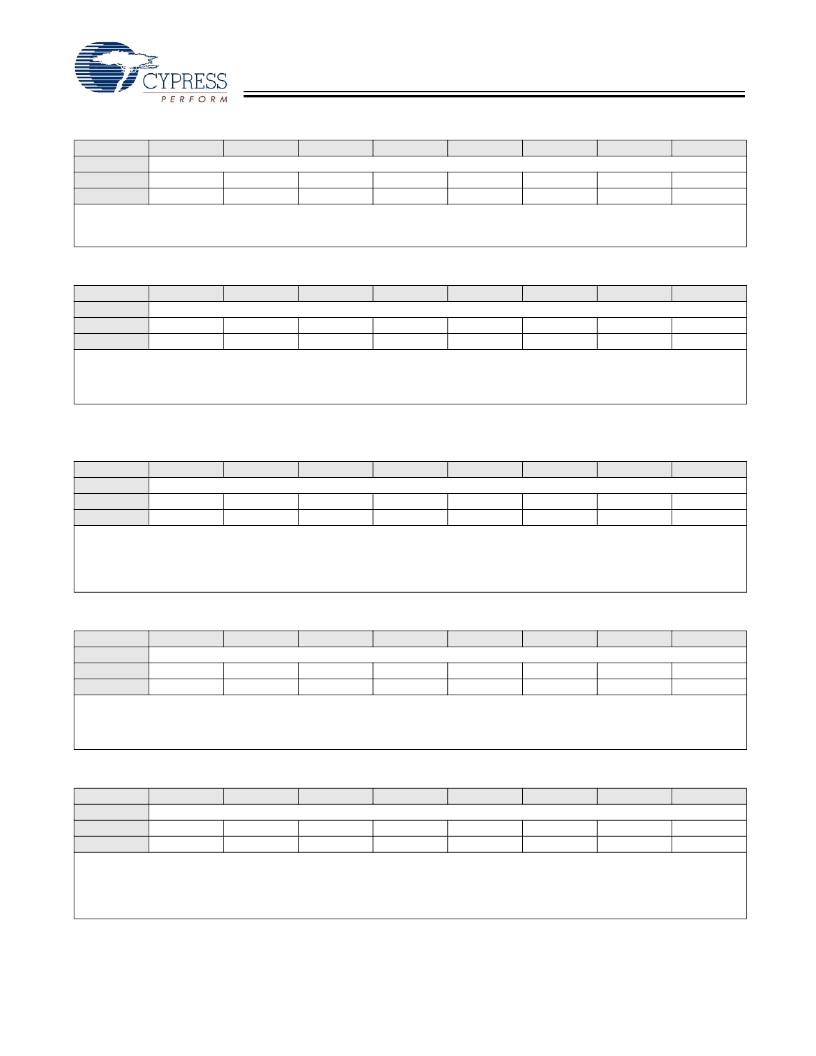

Table 16-2. Free-running Timer High-order Byte (FRTMRH) [0x21] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Free-running Timer [15:8]

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit [7:0]:

Free-running Timer [15:8]

When reading the Free-running Timer, the low-order byte must be read first and the high-order second. When writing, the low-

order byte must be written first then the high-order byte

Table 16-3. Timer Capture 0 Rising (TCAP0R) [0x22] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Capture 0 Rising [7:0]

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit [7:0]:

Capture 0 Rising [7:0]

This register holds the value of the Free-running Timer when the last rising edge occurred on the TCAP0 input. When Capture 0

is in 8-bit mode, the bits that are stored here are selected by the Prescale [2:0] bits in the Timer Configuration register. When

Capture 0 is in 16-bit mode this register holds the lower order 8 bits of the 16-bit timer

Table 16-4. Timer Capture 1 Rising (TCAP1R) [0x23] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Capture 1 Rising [7:0]

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit [7:0]:

Capture 1 Rising [7:0]

This register holds the value of the Free-running Timer when the last rising edge occurred on the TCAP1 input. The bits that are

stored here are selected by the Prescale [2:0] bits in the Timer Configuration register. When Capture 0 is in 16-bit mode this

register holds the high-order 8 bits of the 16-bit timer from the last Capture 0 rising edge. When Capture 0 is in 16-bit mode this

register will be loaded with high-order 8 bits of the 16-bit timer on TCAP0 rising edge

Table 16-5. Timer Capture 0 Falling (TCAP0F) [0x24] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Capture 0 Falling [7:0]

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit [7:0]:

Capture 0 Falling [7:0]

This register holds the value of the Free-running Timer when the last falling edge occurred on the TCAP0 input. When Capture

0 is in 8-bit mode, the bits that are stored here are selected by the Prescale [2:0] bits in the Timer Configuration register. When

Capture 0 is in 16-bit mode this register holds the lower-order 8 bits of the 16-bit timer

Table 16-6. Timer Capture 1 Falling (TCAP1F) [0x25] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Capture 1 Falling [7:0]

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit [7:0]:

Capture 1Falling [7:0]

This register holds the value of the Free-running Timer when the last falling edge occurred on the TCAP1 input. The bits that

are stored here are selected by the Prescale [2:0] bits in the Timer Configuration register. When capture 0 is in 16-bit mode this

register holds the high-order 8 bits of the 16-bit timer from the last Capture 0 falling edge. When Capture 0 is in 16-bit mode this

register will be loaded with high-order 8 bits of the 16-bit timer on TCAP0 falling edge

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C65640-LFXC | TetraHub High-speed USB Hub Controller |

| CY7C65640 | TetraHub High-speed USB Hub Controller |

| CY7C65640-LFC | TetraHub High-speed USB Hub Controller |

| CY4602 | TetraHub High-speed USB Hub Controller |

| CY7C65640A | TetraHub High-Speed USB Hub Controller(TetraHub高速USB Hub控制器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C638334-LTXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C638335-LFXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C638335-LTXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C63833-LFXC | 功能描述:USB 接口集成電路 8K Flash 256 byte RAM COM RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| CY7C63833-LTXC | 功能描述:USB 接口集成電路 USB Peripheral Cntrl 8K/256 32-QFN RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。