- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379097 > CY8C22213-24SIT (CYPRESS SEMICONDUCTOR CORP) PSoC Mixed Signal Array PDF資料下載

參數(shù)資料

| 型號: | CY8C22213-24SIT |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | PSoC Mixed Signal Array |

| 中文描述: | MULTIFUNCTION PERIPHERAL, PDSO20 |

| 封裝: | 0.300 INCH, MO-119, SOIC-20 |

| 文件頁數(shù): | 73/304頁 |

| 文件大小: | 2956K |

| 代理商: | CY8C22213-24SIT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當(dāng)前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁第265頁第266頁第267頁第268頁第269頁第270頁第271頁第272頁第273頁第274頁第275頁第276頁第277頁第278頁第279頁第280頁第281頁第282頁第283頁第284頁第285頁第286頁第287頁第288頁第289頁第290頁第291頁第292頁第293頁第294頁第295頁第296頁第297頁第298頁第299頁第300頁第301頁第302頁第303頁第304頁

December 22, 2003

Document No. 38-12009 Rev. *D

73

12.

Sleep and Watchdog

This chapter discusses the Sleep and Watchdog operations and its associated registers.

The goal of sleep operation is to reduce average power con-

sumption as much as possible. The system has a sleep

state that can be initiated under firmware control. In this

state, the CPU is stopped at an instruction boundary and the

24/48 MHz oscillator, the Flash memory module, and band-

gap-voltage reference are powered down. The only blocks

that remain in operation are the 32 kHz oscillator (external

crystal or internal), PSoC blocks clocked from the 32 kHz

clock selection, and the supply voltage monitor circuit.

Analog PSoC blocks have individual power down settings

that are controlled by firmware, independently of the sleep

state. Continuous time analog blocks may remain in opera-

tion, since they do not require a clock source. Typically,

however, switched capacitor analog blocks will not operate

since the internal sources of clocking for these blocks are

stopped.

The system can only wake up from sleep as a result of an

interrupt or reset event. The Sleep timer can provide peri-

odic interrupts to allow the system to wake up, poll peripher-

als, or do real-time functions and then go to sleep again.

GPIO (pin) interrupts, supply monitor interrupt, analog col-

umn interrupts, and timers clocked externally or from the 32

kHz clock are examples of asynchronous interrupts that can

also be used to wake the system up.

The Watchdog Timer (WDT) circuit is designed to assert a

hardware reset to the device after a pre-programmed inter-

val, unless it is periodically serviced in firmware. This func-

tionality serves to reboot the system in the event of a CPU

crash. It can also restart the system from the CPU halt state.

Once the WDT is enabled, it can only be disabled by an

external reset (XRES) or a power on reset (POR). A WDT

reset will leave the WDT enabled. Therefore, if the WDT is

used in an application, all code (including initialization code)

must be written as though the WDT is enabled.

12.1

Architectural Description

Device components that are involved in sleep and watchdog

operation are the selected 32 kHz clock (external crystal or

internal), the Sleep timer, the sleep bit in the CPU_SCR0

register, the sleep circuit (to sequence going into and com-

ing out of sleep), the band gap refresh circuit (to periodically

refresh the reference voltage during sleep), and the Watch-

dog timer.

12.1.1

32 kHz Clock Selection

By default, the 32 kHz clock source is the Internal Low-

Speed Oscillator (ILO). Optionally, the External Crystal

Oscillator (ECO) may be activated. This selection is made in

bit 7 of the OSC_CR0 register. Selecting the ECO as the

active source for the 32 kHz clock allows the Sleep timer

and sleep interrupt to be used in real-time applications.

Regardless of the clock source selected, the 32 kHz clock

plays a key role in sleep functionality. It runs continuously

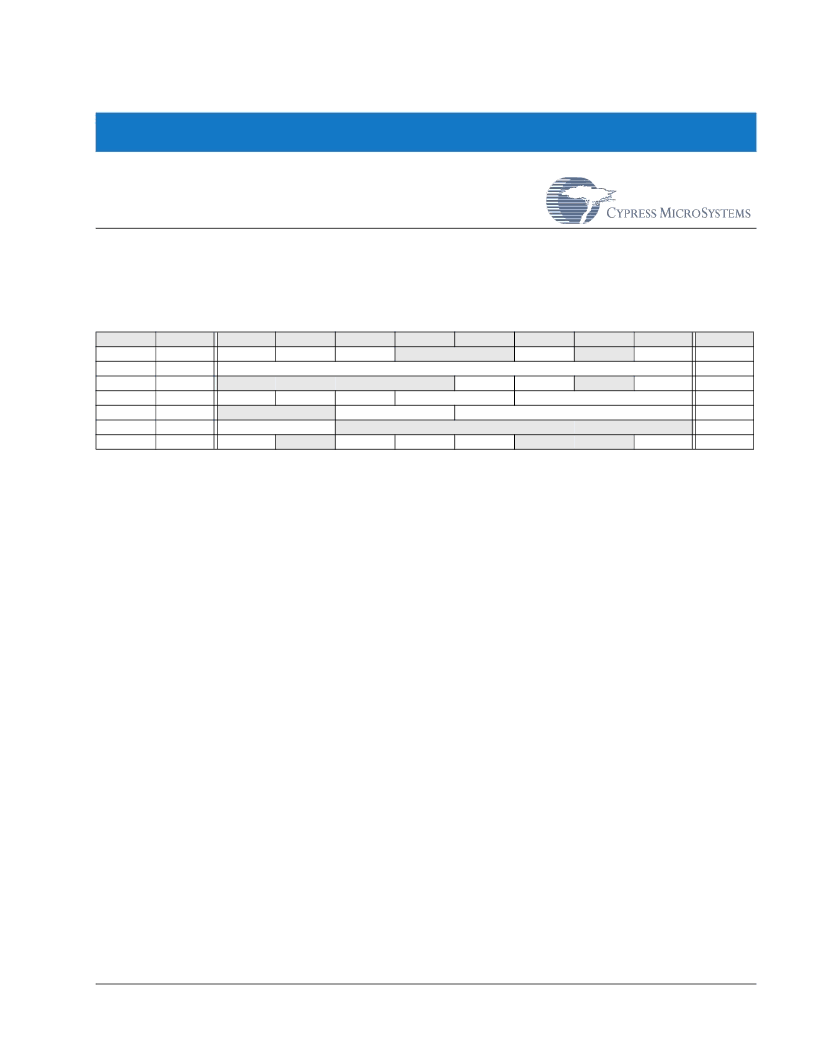

Table 12-1. Sleep and Watchdog Registers

Address

0,E0h

0,E3h

x,FEh

1,E0h

1,E9h

1,EBh

x,FFh

LEGEND

X: The value for power on reset is unknown.

x: An “x” before the comma in the address field indicates that this register can be accessed or written to no matter what bank is used.

*: This bit is read only.

Name

Bit 7

VC3

Bit 6

Sleep

Bit 5

GPIO

Bit 4

Bit 3

Bit 2

Analog 1

Bit 1

Bit 0

V Monitor

Access

RW : 00

W : 00

RW : 00

RW : 00

W : 00

W : 00

W : XX

INT_MSK0

RES_WDT

CPU_SCR1

OSC_CR0

ILO_TR

ECO_TR

CPU_SCR0

WDSL_Clear

ECO EXW

ECO EX

IRAMDIS

32k Select

PLL Mode

No Buzz

Sleep[1:0]

CPU Speed[2:0]

Freq Trim[3:0]

Bias Trim[1:0]

PSSDC[1:0]

GIES

WDRS

PORS

Sleep

STOP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY8C24794-SPAX | PSoCTM Mixed-Signal Array |

| CY8C24794-SPE | PSoCTM Mixed-Signal Array |

| CY8C24794-SPI | Explosion-Proof Limit Switches Series CX: Short Housing: Top Plunger; 1NC 1NO SPDT Snap Action; Number of internal basic switches BZ: 1; 0.75 in - 14NPT conduit |

| CY8C24794-SPLFX | Environmentally sealed limit switch with Leadwire termination, Rotary Roller Lever actuation, Double Pole Double Throw (DPDT) Circuitry, 5 A (Resistive) ampere rating at 28 Vdc, Military Part Number MS21320-1 |

| CY8C24794-SPPVX | Environmentally sealed limit switch with Leadwire termination, Rotary Roller Lever actuation, Double Pole Double Throw (DPDT) Circuitry, 5 A (Resistive) ampere rating at 28 Vdc, Military Part Number MS21320-2 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY8C22345 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:PSoC Programmable System-on-Chip |

| CY8C22345-12PVXE | 功能描述:可編程片上系統(tǒng) - PSoC M8C 8bit Flash 16KB RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:67 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風(fēng)格:SMD/SMT |

| CY8C22345-12PVXET | 功能描述:可編程片上系統(tǒng) - PSoC M8C 8bit Flash 16KB RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:67 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風(fēng)格:SMD/SMT |

| CY8C22345-24PVXA | 功能描述:可編程片上系統(tǒng) - PSoC 24 I/O 16K FLASH 1K SRAM RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:67 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風(fēng)格:SMD/SMT |

| CY8C22345-24PVXAT | 功能描述:可編程片上系統(tǒng) - PSoC 24 I/O 16K FLASH 1K SRAM RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:67 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。