- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379184 > DS3153N Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs PDF資料下載

參數(shù)資料

| 型號(hào): | DS3153N |

| 英文描述: | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

| 中文描述: | 單/雙/三/四DS3/E3/STS-1柳斯 |

| 文件頁(yè)數(shù): | 30/60頁(yè) |

| 文件大小: | 788K |

| 代理商: | DS3153N |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

DS3151/DS3152/DS3153/DS3154 Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs

30 of 60

the JA must take its master clock from the MCLK pin. The clock and data recovery block also uses the selected

master clock.

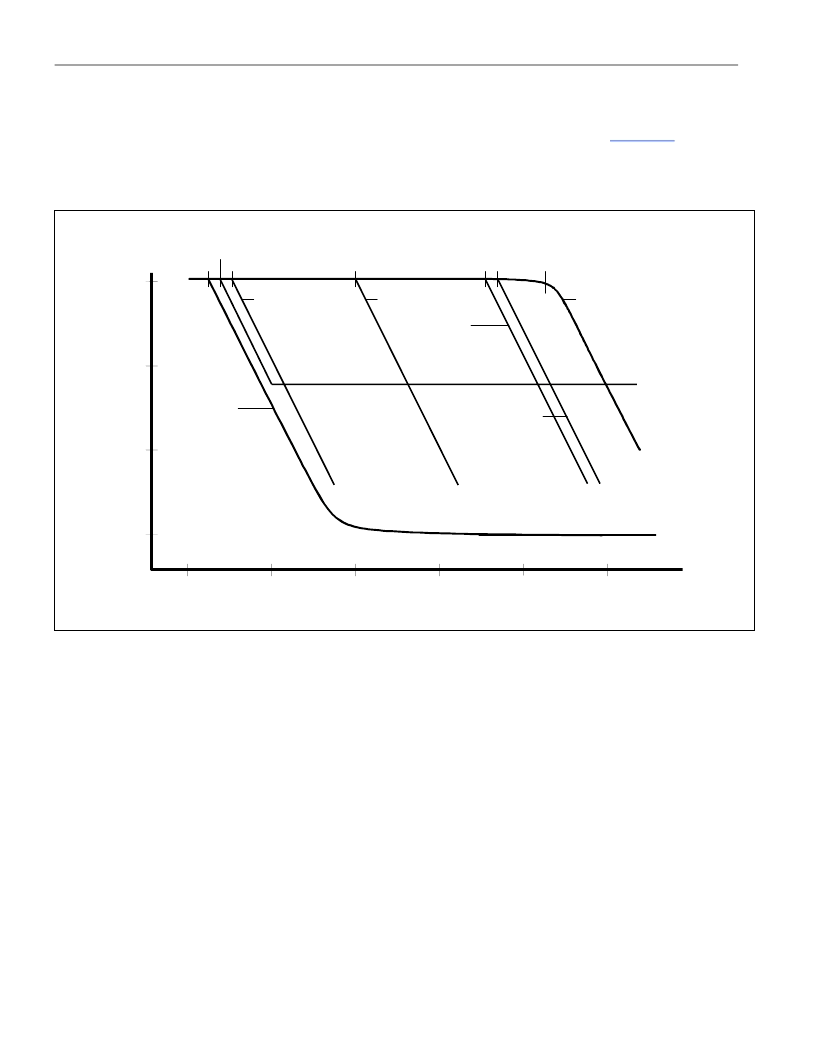

The JA has a loop bandwidth of master_clock / 2,058,874 (see corner frequencies in

Figure 9-1

). The JA

attenuates jitter at frequencies higher than the loop bandwidth, while allowing jitter (and wander) at lower

frequencies to pass through relatively unaffected.

Figure 9-1. Jitter Attenuation/Jitter Transfer

10.

RESET LOGIC

There are four sources for reset: an internal power-on reset (POR) circuit, the reset pin

RST

, the JTAG reset pin

JTRST

, and the RST bit in each LIU’s global configuration register (GCR). The chip is divided into three zones for

reset: the digital logic, the analog circuits, and the JTAG logic. The digital logic includes the status and control

registers, the B3ZS/HDB3 encoder and decoder, the PRBS generator and detector, and the LOS detect logic. The

analog circuits include clock and data recovery, jitter attenuator, and transmit waveform generation. The JTAG

logic consists of the common boundary scan controller and the boundary scan cells at each pin.

The POR circuit resets the digital logic, analog circuits, and JTAG logic zones. The

RST

pin resets the digital logic

and the analog circuits but not the JTAG logic. The

JTRST

pin resets only the JTAG logic. Each LIU’s RST register

bit resets the digital logic for that LIU, including resetting the LIU’s registers to the default state (except for the RST

bit).

The POR signal and

RST

pin require an active master clock source for the LIU to properly reset.

10

100

1k

10k

100k

1M

21.7Hz (DS3)

16.7Hz (E3)

25.2Hz (STS-1)

1k

-30

-20

-10

E3 [TBR24 (1997)]

FREQUENCY (Hz)

J

0

DS3 [GR-499 (1995)]

CATEGORY I

DS315x TYPICAL RECEIVER

JITTER TRANSFER WITH JITTER

ATTENUATOR DISABLED

>150k

DS315x

DS3/E3/STS-1

MINIMUM

JITTER

ATTENUATION

WITH JITTER

ATTENUATOR

ENABLED

40Hz

DS3 [GR-253 (1999)]

CATEGORY I

27Hz

STS-1 [GR-253

(1999)]

CATEGORY II

40k 59.6k

DS3 [GR-499 (1999)]

CATEGORY II

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS3154 | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

| DS3154N | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

| DS3154DK | Quad DS3/E3/STS-1 LIU Demo Kit |

| DS32KHZ | 32.768kHz Temperature-Compensated Crystal Oscillator |

| DS32kHz-N | 32.768kHz Temperature-Compensated Crystal Oscillator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3153N# | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Triple DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3153N+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Triple DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3154 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Quad DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3154+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Quad DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3154A2 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Quad DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。