- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362741 > EP224-10A (Altera Corporation) Classic EPLDs PDF資料下載

參數(shù)資料

| 型號: | EP224-10A |

| 廠商: | Altera Corporation |

| 英文描述: | Classic EPLDs |

| 中文描述: | 經(jīng)典EPLDs |

| 文件頁數(shù): | 3/16頁 |

| 文件大小: | 265K |

| 代理商: | EP224-10A |

Altera Corporation

3

EP220 & EP224 Classic EPLDs

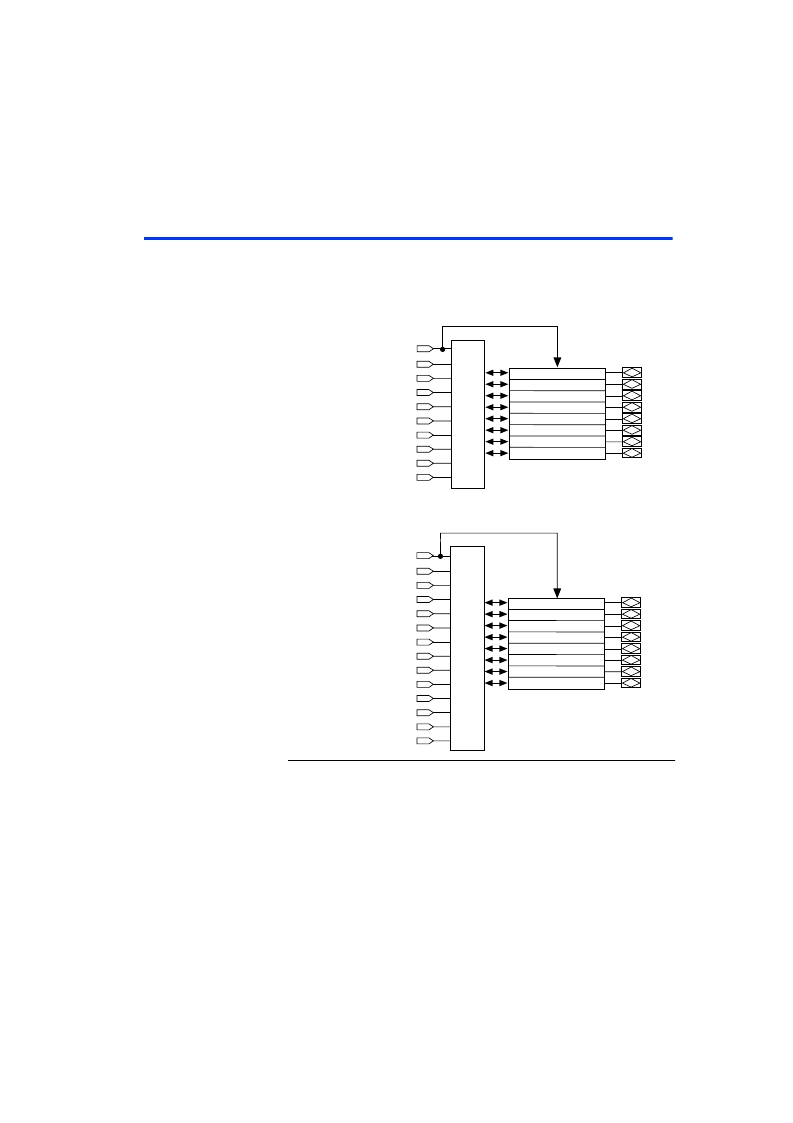

Figure 1. EP220 & EP224 Block Diagram

Numbers in parentheses refer to the pin-out number

The EP220 and EP224 architecture is based on a sum-of-products,

programmable-

AND

/fixed-

OR

structure. Each macrocell can be

individually programmed for combinatorial or registered output. An

inversion option allows each output to be configured for active-high or

active-low operation. Each I/O pin can be programmed to function as an

input, output, or bidirectional pin.

The EP220 and EP224 device architecture offers the following features:

I

I

Macrocells

High-frequency, low-skew global Clock

EP220

I/O (19)

I/O (18)

I/O (17)

I/O (16)

I/O (15)

I/O (14)

I/O (13)

I/O (12)

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Global Clock

Global

Bus

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(11)

INPUT/CLK

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

EP224

Global

Bus

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Global Clock

I/O (22)

I/O (21)

I/O (20)

I/O (19)

I/O (18)

I/O (17)

I/O (16)

I/O (15)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

(11)

(13)

(14)

(23)

INPUT/CLK

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

相關PDF資料 |

PDF描述 |

|---|---|

| EP224-12 | Classic EPLDs |

| EP224-7 | Classic EPLDs |

| EP224LC-10 | Classic EPLDs |

| EP224LC-10A | Classic EPLDs |

| EP224LC-12 | Classic EPLDs |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EP224-12 | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Classic EPLDs |

| EP224-7 | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Classic EPLDs |

| EP224DC10A | 制造商:ALTERA 功能描述:* |

| EP224DC-10A | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP224DC-12 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。