- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362742 > EP7209 (Cirrus Logic, Inc.) Ultra-Low-Power Audio Decoder System-on-Chip PDF資料下載

參數(shù)資料

| 型號: | EP7209 |

| 廠商: | Cirrus Logic, Inc. |

| 英文描述: | Ultra-Low-Power Audio Decoder System-on-Chip |

| 中文描述: | 超低功耗音頻解碼器系統(tǒng)級芯片 |

| 文件頁數(shù): | 36/128頁 |

| 文件大小: | 1382K |

| 代理商: | EP7209 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

EP7209

36

DS453PP2

3.11.1

Codec Sound Interface

The codec interface allows direct connection of a

telephony type codec to the EP7209. It provides all

the necessary clocks and timing pulses and per-

forms a parallel to serial conversion or vice versa

on the data stream to or from the external codec de-

vice. The interface is full duplex and contains two

separate data FIFOs (16 deep by 8-bits wide, one

for the receive data, another for the transmit data).

Data is transferred to or from the codec at

64 kbits/s. The data is either written to or read from

the appropriate 16 byte FIFO. If enabled, a codec

interrupt (CSINT) will be generated after every

8 bytes are transferred (FIFO half full/empty). This

means the interrupt rate will be every 1 msec, with

a latency of 1 msec.

Transmit and receive modes are enabled by assert-

ing high both the CDENRX and CDENTX codec

enable bits in the SYSCON1 register.

NOTE:

Both the CDENRX and CDENTX enable bits

should be asserted in tandem for data to be

transmitted or received. The reason for this

is that the interrupt generation will occur

1 msec after one of the FIFOs is enabled.

For example: If the receive FIFO gets

enabled first and the transmit FIFO at a later

time, the interrupt will occur 1 msec after the

receive FIFO is enabled. After the first inter-

rupt occurs, the receive FIFO will be half full.

However, it will not be possible to know how

full the transmit FIFO will be since it was

enabled at a later time. Thus, it is possible to

unintentionally overwrite data already in the

transmit FIFO (See

Figure 6

).

After the CDENRX and CDENTX enable bits get

asserted, the corresponding FIFOs become en-

abled. When both FIFOs are disabled, the FIFO sta-

tus flag CRXFE is set and CTXFF is cleared so that

the FIFOs appear empty. Additionally, if the

CDENTX bit is low, the PCMOUT output is dis-

abled. Asserting either of the two enable bits causes

the sync and interrupt generation logic to become

active; otherwise they are disabled to conserve

power.

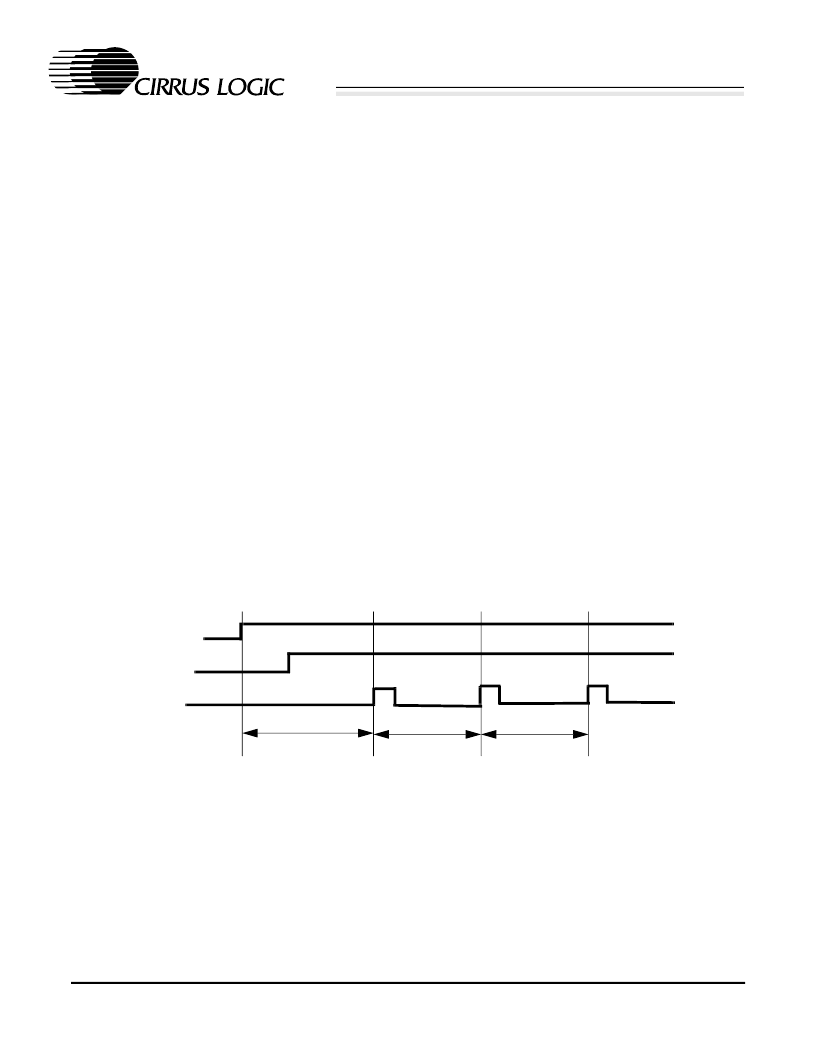

CDENRX

CDENTX

CSINT

1 ms

1 ms

1 ms

I

I

I

Figure 6. Codec Interrupt Timing

相關PDF資料 |

PDF描述 |

|---|---|

| EP7211 | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CP-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CV-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7212 | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

| EP7212-CB-A | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EP7209-CB-D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP7209-CV-D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP7211 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211(208LQFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| EP7211(256PBGA) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。