- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362742 > EP7211 (Cirrus Logic, Inc.) HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | EP7211 |

| 廠商: | Cirrus Logic, Inc. |

| 英文描述: | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| 中文描述: | 高性能超低功耗系統(tǒng)與LCD控制器芯片 |

| 文件頁數(shù): | 122/166頁 |

| 文件大?。?/td> | 2623K |

| 代理商: | EP7211 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁當(dāng)前第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁

EP7211

High-Performance Ultra-Low-Power System-on-Chip with LCD Controller

122

Register Descriptions

DS352PP3

JUL 2001

5.16.2.2

MCP Data Register 1

ADDRESS: 0x8000.2080

When MPC Data Register 1 (MCDR1) is read, the bottom entry of the telecom receive FIFO is

accessed. As data is removed by the MCP

’

s receive logic from the incoming data frame, it is placed

into the top entry of the telecom receive FIFO and is transferred down an entry at a time until it

reaches the last empty location within the FIFO. Data is removed by reading MCDR1, which

accesses the bottom entry of the telecom FIFO. After MCDR1 is read, the bottom entry is

invalidated, and all remaining values within the FIFO automatically transfer down one location.

When MCDR1 is written, the top-most entry of the telecom transmit FIFO is accessed. After a write,

data is automatically transferred down to the lowest location within the transmit FIFO which does

not already contain valid data. Data is removed from the bottom of the FIFO one value at a time by

the transmit logic. It is then loaded into the correct position within the 64-bit transmit serial shifter

then serially shifted out onto the

SIBDOUT

pin during subframe 0.

Telecom data is 14-bits wide and must be left justified by the user before writing them to the transmit

FIFO (MSB of telecom data corresponds to bit 16 of transmit FIFO). The lower two bits of the FIFO

which are aligned within the 16-bit value are also written to MCDR1 for transmission. The UCB1100

automatically forces bits 0 and 1 to zero before transmitting the value to the MCP. The user must

right justify received telecom data before using it.

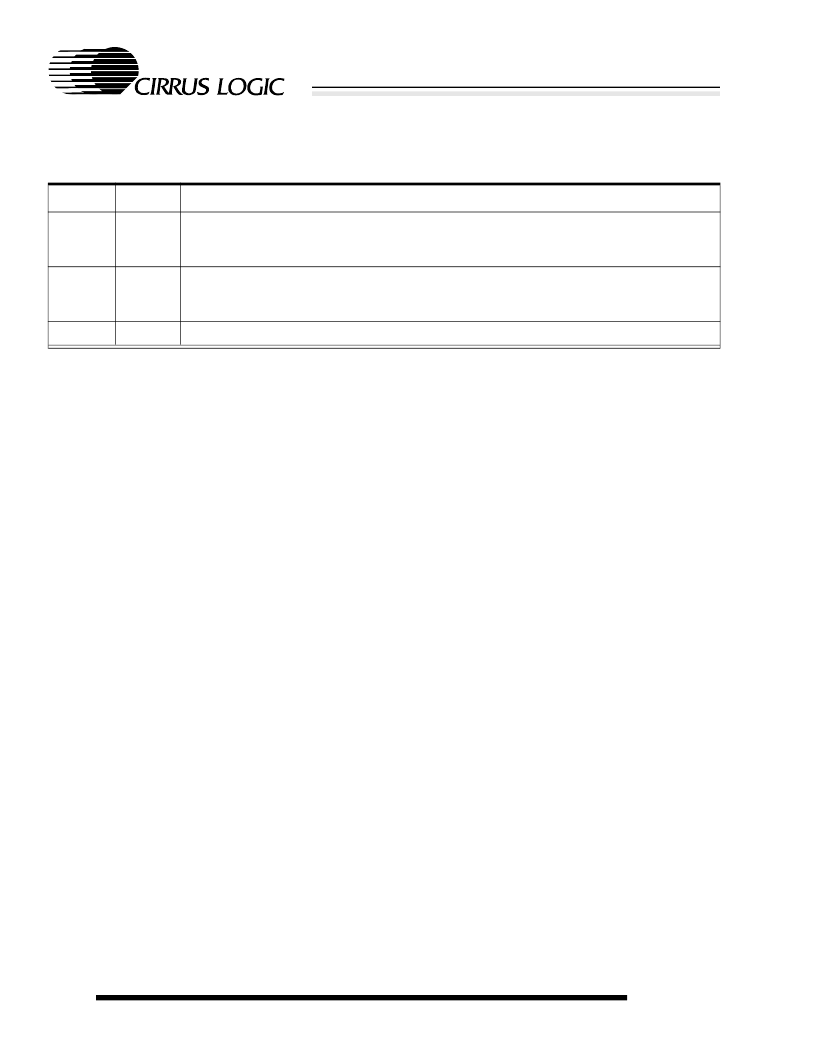

Table 5-14. MCP Data Register 0

Bit

Name

Description

3

–

0

—

Reserved for future enhancements

Read

—

Data returned, but UCB1100 currently zero fills these four bits

Write

—

MCP

’

s transmit logic sends these bits, even though they are ignored by the UCB1100

15

–

4

Audio

Data

Transmit/Receive Audio FIFO Data

Read

—

Bottom of Audio Receive FIFO data

Write

—

Top of Audio Transmit FIFO data

31

–

16

—

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP7211-CP-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CV-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7212 | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

| EP7212-CB-A | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

| EP7212-CV-A | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP7211(208LQFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| EP7211(256PBGA) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| EP7211-CB-D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP7211-CP-A | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CV-A | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。