- 您現(xiàn)在的位置:買賣IC網 > PDF目錄353093 > EPF10K50S Programmable Logic PDF資料下載

參數(shù)資料

| 型號: | EPF10K50S |

| 英文描述: | Programmable Logic |

| 中文描述: | 可編程邏輯 |

| 文件頁數(shù): | 22/138頁 |

| 文件大小: | 2116K |

| 代理商: | EPF10K50S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

118

Altera Corporation

FLEX 10K Embedded Programmable Logic Family Data Sheet

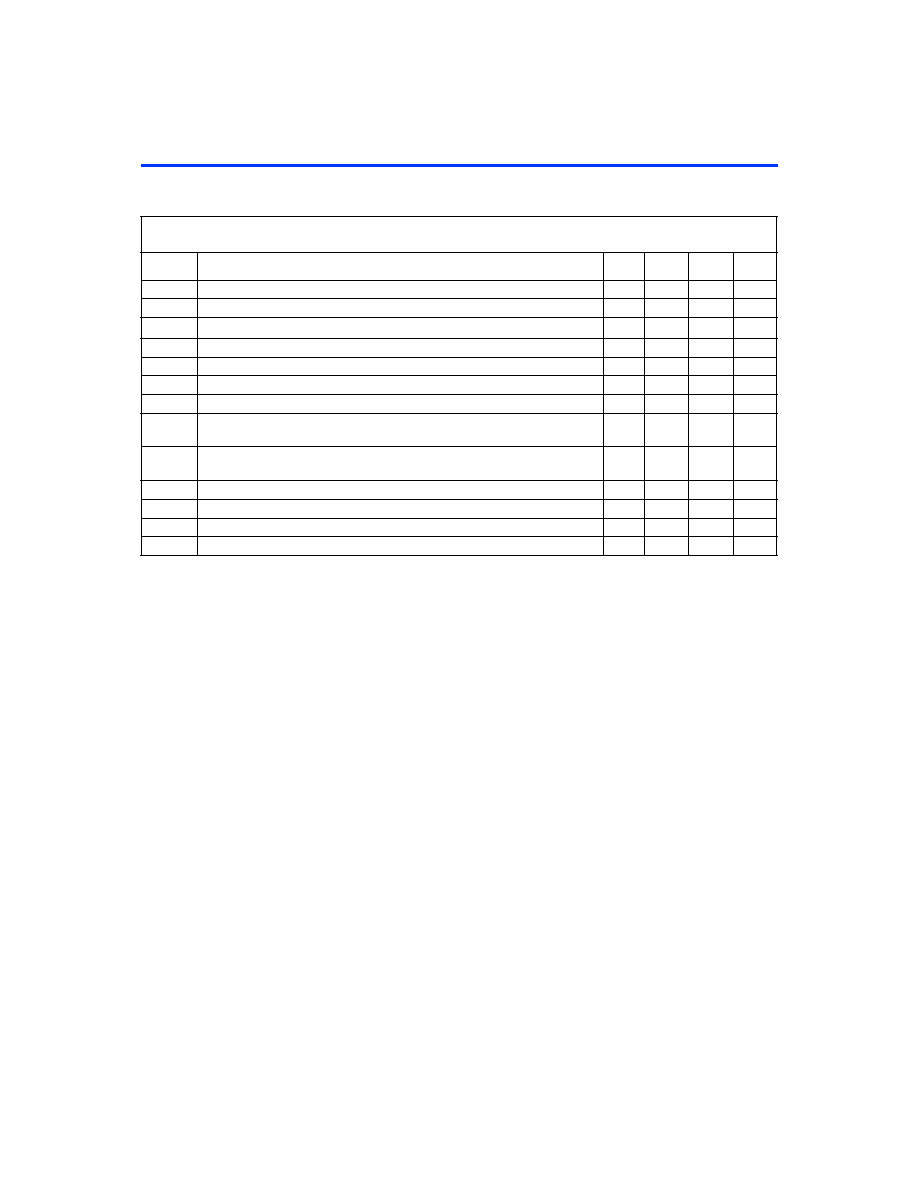

Table 114 summarizes the ClockLock and ClockBoost parameters.

Notes:

(1)

To implement the ClockLock and ClockBoost circuitry with the MAX+PLUS II software, designers must specify the

input frequency. The MAX+PLUS II software tunes the PLL in the ClockLock and ClockBoost circuitry to this

frequency. The fCLKDEV parameter specifies how much the incoming clock can differ from the specified frequency

during device operation. Simulation does not reflect this parameter.

(2)

During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If

the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during

configuration, because the tLOCK value is less than the time required for configuration.

(3)

The tJITTER specification is measured under long-term observation.

Power

Consumption

The supply power (P) for FLEX 10K devices can be calculated with the

following equation:

P = PINT + PIO = (ICCSTANDBY + ICCACTIVE) × VCC + PIO

Typical ICCSTANDBY values are shown as ICC0 in the FLEX 10K 5.0-V

sheet. The ICCACTIVE value depends on the switching frequency and the

application logic. This value is calculated based on the amount of current

that each LE typically consumes. The PIO value, which depends on the

device output load characteristics and switching frequency, can be

calculated using the guidelines given in Application Note 74 (Evaluating

Table 114. ClockLock & ClockBoost Parameters

Symbol

Parameter

Min

Typ

Max

Unit

tR

Input rise time

2

ns

tF

Input fall time

2

ns

tINDUTY

Input duty cycle

45

55

%

fCLK1

Input clock frequency (ClockBoost clock multiplication factor equals 1)

30

80

MHz

tCLK1

Input clock period (ClockBoost clock multiplication factor equals 1)

12.5

33.3

ns

fCLK2

Input clock frequency (ClockBoost clock multiplication factor equals 2)

16

50

MHz

tCLK2

Input clock period (ClockBoost clock multiplication factor equals 2)

20

62.5

ns

fCLKDEV1 Input deviation from user specification in MAX+PLUS II (ClockBoost clock

multiplication factor equals 1)

±1

MHz

fCLKDEV2 Input deviation from user specification in MAX+PLUS II (ClockBoost clock

multiplication factor equals 2)

±0.5

MHz

tINCLKSTB Input clock stability (measured between adjacent clocks)

100

ps

tLOCK

Time required for ClockLock or ClockBoost to acquire lock

10

s

tJITTER

Jitter on ClockLock or ClockBoost-generated clock

1

ns

tOUTDUTY Duty cycle for ClockLock or ClockBoost-generated clock

40

50

60

%

相關PDF資料 |

PDF描述 |

|---|---|

| EPF10K50SQC240-2 | Field Programmable Gate Array (FPGA) |

| EPF10K50SQC240-2X | Field Programmable Gate Array (FPGA) |

| EPA810-80 | Tapped Delay Line |

| EPA810-800 | Tapped Delay Line |

| EPA810-85 | Tapped Delay Line |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EPF10K50SBC356-1 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 10K 360 LABs 220 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF10K50SBC356-1X | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 10K 360 LABs 220 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF10K50SBC356-2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 10K 360 LABs 220 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF10K50SBC356-2X | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 10K 360 LABs 220 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF10K50SBC356-3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 10K 360 LABs 220 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。