- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄44009 > LK1001-9EPD8 (POWER-ONE INC) 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE PDF資料下載

參數(shù)資料

| 型號: | LK1001-9EPD8 |

| 廠商: | POWER-ONE INC |

| 元件分類: | 電源模塊 |

| 英文描述: | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| 封裝: | HEAT SINK, METAL, CASE K02, MODULE |

| 文件頁數(shù): | 16/27頁 |

| 文件大?。?/td> | 640K |

| 代理商: | LK1001-9EPD8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

K-Family

DC-DC Converters >100 W

Rugged Environment

8 - 24

Edition 2/96 - Melcher AG

MELCHER

The Power Partners.

8.1

Formula for the external input capacitor:

2

Po (t h + 0.3 ms) 100

Ci ext = –––––––––––––––––––––– – Ci min

η (U

ti

2 – Ui min2)

where as:

C i min = internal input capacitance [mF]

C i ext = external input capacitance [mF]

Po

= output power [W]

η

= efficiency [%]

t h

= hold-up time [ms]

U i min = minimum input voltage [V] 1

U ti

= threshold level [V]

1 Min. input voltage according to "Electrical Input Data". For out-

put voltages

Uo > Uo nom, the minimum input voltage increases

proportionally to

Uo/Uo nom.

Remarks:

Option V2 and V3 can be adjusted by potentiometer to a

threshold level between

Ui min and Ui max. A decoupling di-

ode should be connected in series with the input of AK...FK

converters to avoid the input capacitance discharging

through other loads connected to the same source voltage.

Option V ACFAIL signal (VME)

This option defines an undervoltage monitoring circuit for

the input or input and main output voltage (

Uo1 nom = 5.1 V

only) equivalent to option D and generates an ACFAIL sig-

nal (V signal) which conforms to the VME standard.

The low state level of the ACFAIL signal is specified at a

sink current of

IV ≤ 48 mA to UV ≤ 0.6 V (open-collector out-

put of a NPN transistor). The pull-up resistor feeding the

open-collector output should be placed on the VME back

plane.

After the ACFAIL signal has gone low, the VME standard

requires a hold-up time

t h of at least 4 ms before the 5.1 V

output drops to 4.875 V when the output is fully loaded.

This hold-up time

t h is provided by the internal input capaci-

tance. Consequently the working input voltage and the

threshold level

U ti should be adequately above the mini-

mum input voltage

Ui min of the converter so that enough

energy is remaining in the input capacitance. If the input

voltage is below the required level, an external hold-up ca-

pacitor (

Ci ext) should be added.

Formula for threshold level for desired value of

th:

2

Po (t h + 0.3 ms) 100

Uti =

––––––––––––––––––––– +

Ui min2

Ci min

η

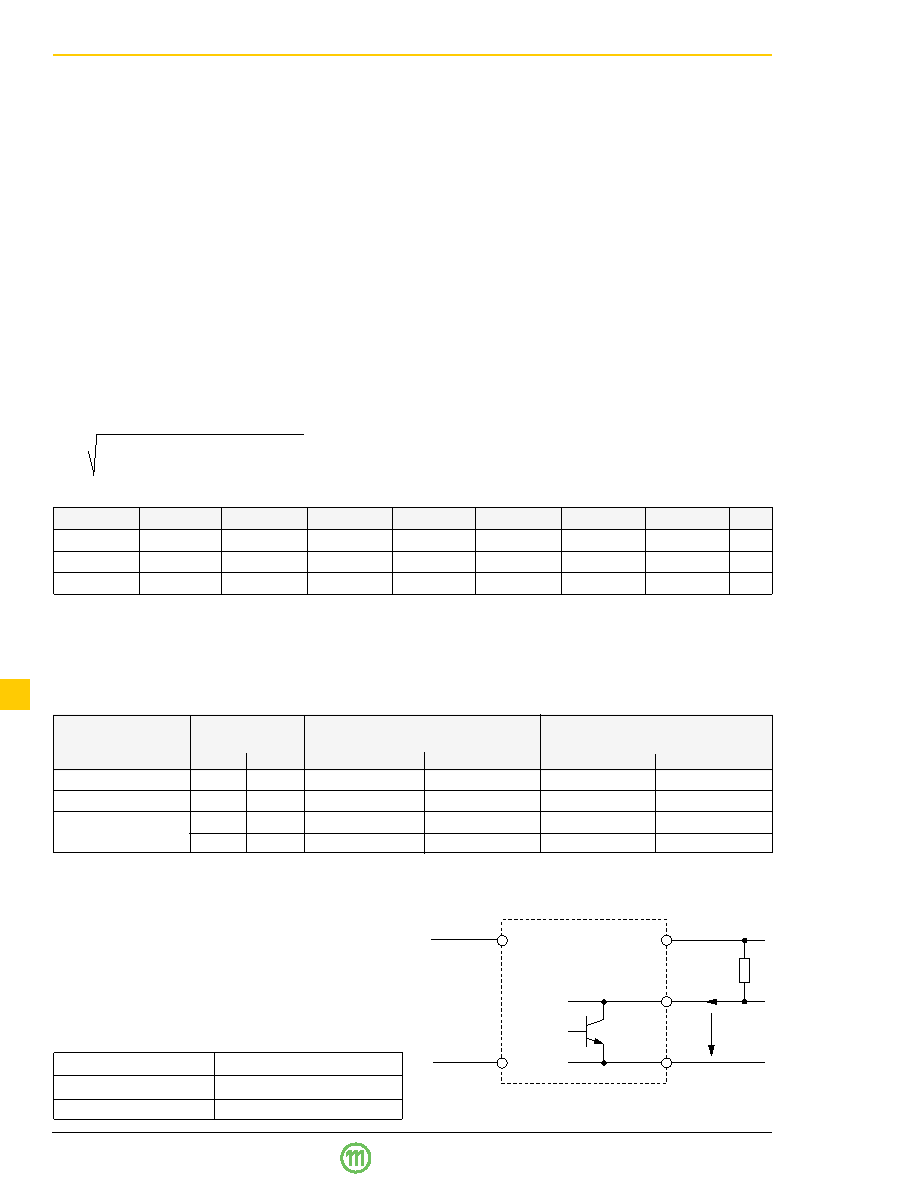

V output (V0, V2, V3):

Connector pin V is internally connected to the open collec-

tor of a NPN transistor. The emitter is connected to the

negative potential of output 1.

U V ≤ 0.6 V (logic low) corre-

sponds to a monitored voltage level (

Ui and/or Uo1) <Ut.

The current

I V through the open collector should not exceed

50 mA. The NPN output is not protected against external

overvoltages.

U V should not exceed 60 V.

Ui, Uo1 status

V output,

UV

Ui or Uo1 < Ut

low, L,

UV

≤ 0.6 V at IV = 50 mA

Ui and Uo1 > Ut + Uh

high, H,

I V

≤ 25 A at UV = 5.1 V

Fig. 28

Output configuration of options V0, V2 and V3

Vo1+

Vo1–

V

UV

IV

Vi+

Vi–

RP

Table 18: Undervoltage monitor functions

V output

Monitoring

Minimum adjustment range

Typical hysteresis

Uh [% of Ut]

(VME compatible)

of threshold level

Ut

for

Ut min…Ut max

Ui

Uo1

Uti

Uto

Uhi

Uho

V2

yes

no

Ui min...Ui max 1–

3.4...0.4

–

V3

yes

Ui min...Ui max 1

0.95...0.985

Uo1 2

3.4...0.4

"0"

V0

yes

no

Ui min...Ui max 3 4

–

3.4...0.4

–

yes

Ui min...Ui max 3 4

0.95...0.985

Uo1 2

3.4...0.4

"0"

1 Threshold level adjustable by potentiometer. 2 Fixed value between 95% and 98 .5% of Uo1 (tracking). 3 Adjusted at Io nom.

4 Fixed value, resistor-adjusted (

±2% at 25°C) acc. to customer's specifications; individual type number is determined by Melcher.

voltage(s) exceed(s)

Ut + Uh. The threshold level Uti is ei-

ther adjustable by potentiometer, accessible through a hole

in the front cover, or adjusted during manufacture to a de-

termined customer specified value.

Versions V0, V2 and V3 are available as shown below.

Option V operates independently of the built-in input under-

voltage lock-out circuit. A logic "low" signal is generated at

pin 20 as soon as one of the monitored voltages drops be-

low the preselected threshold level

Ut. The return for this

signal is Vo1–. The V output recovers when the monitored

Table 17: Available internal input capacitance and factory potentiometer setting of Uti with resulting hold-up time

Types

AK

BK

FK

CK

DK

EK

LK

Unit

Ci min

0.83

0.3

1.2

0.66

0.26

0.21

mF

Ut i

9.5

19.5

39

61

97

120

V DC

th

0.1

3.4

1.1

2.7

4.2

ms

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LK1001-9ERD7 | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| LK1301-9EPD3B1 | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| LK1501-9EPD8TB1 | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| LK1601-9EPD7TB1 | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| LK2320-9EPD1TB1 | 2-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LK1001-9ER | 制造商:Power-One 功能描述:ACDC - Bulk |

| LK100-24P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| LK100-28P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| LK10051R0K-T | 功能描述:固定電感器 INDCTR STD MULTILYR 0402 1uH 10% RoHS:否 制造商:AVX 電感:10 uH 容差:20 % 最大直流電流:1 A 最大直流電阻:0.075 Ohms 工作溫度范圍:- 40 C to + 85 C 自諧振頻率:38 MHz Q 最小值:40 尺寸:4.45 mm W x 6.6 mm L x 2.92 mm H 屏蔽:Shielded 端接類型:SMD/SMT 封裝 / 箱體:6.6 mm x 4.45 mm |

| LK10051R0K-T | 制造商:TAIYO YUDEN 功能描述:Inductor Series:LF LK |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。