- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384398 > HE84G752B (King Billion Electronics Co., Ltd.) 8-BIT MICRO-CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | HE84G752B |

| 廠商: | King Billion Electronics Co., Ltd. |

| 英文描述: | 8-BIT MICRO-CONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁(yè)數(shù): | 38/49頁(yè) |

| 文件大小: | 474K |

| 代理商: | HE84G752B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)

KING BILLION ELECTRONICS CO., LTD

駿

億

電

子

股

份

有

限

公

司

HE84G752B

HE80004 Series

January 21, 2005

This specification is subject to change without notice. Please contact sales person for the latest version before use.

38

V0.93

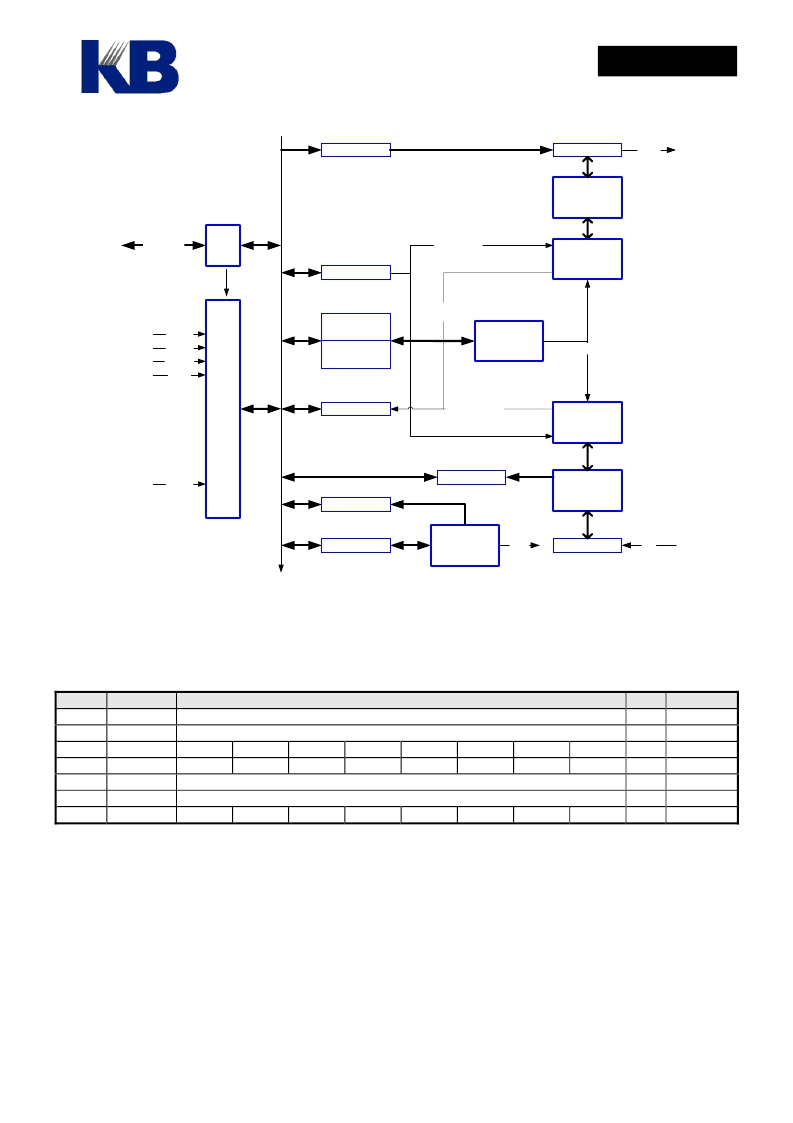

I/F

CTRL

BAUD-RATE

Interrupt Id Reg

Line Status Reg

Line Control Reg

Bus

Buffer

Trans Hoding Reg

Rec Buffer Reg

Div Latch (LS)

Div Latch (MS)

“

Transmitter

control signal

"

INTR

Interrupt

Interrupt En Reg

“

Transmitter

“Receive status"

RESET

EX_PT[7:0]

MCLK

XRD_N

XWR_N

ADS_N

RECEIVE

MACHINE

Rec Shift Reg

TIMING

CAND

TRTIMING

CAND

Trans Shift Reg

SOUT

SIN

BrgClk

coReceiver

"

19.1.

Interface Registers

Addressable extension register used to interface with MCU

Address

Name

00H

RBR

01H

THR

02H

IEIR

0

RLSI

03H

LCR

BRGE

SB

04H

BRL

05H

BRH

06H

LSR

0

TEMT

IEIR: Interrupt enable/disable identification register.

LCR: Line control register.

LSR: Line status register.

19.2.

Baud Rate Configuration Register

Function

Mode

R

R/W

R/W

R/W

R/W

R/W

R

RESET

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0110 0000

UART RECEIVER BUFFER

UART TRANSMITTER HOLDING REGISTER

THRI

RBRI

SP

EPS

UART LSB of Baud Rate Register

UART MSB of Baud Rate Register

THRE

BI

0

ID2

STB

ID1

WLS1

ID0

WLS0

PEN

FE

PE

OE

DR

The BRH and BRL registers hold the upper and lower bytes of 16 bit baud rate divisor and which are

readable/writable. The baud rate of UART is calculated as following:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HE84G761B | 8-BIT MICRO-CONTROLLER |

| HE84G762B | 8-BIT MICRO-CONTROLLER |

| HE84G763B | 8-BIT MICRO-CONTROLLER |

| HE84G770B | 8-BIT MICRO-CONTROLLER |

| HE85750 | 8-bit Micro-controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HE84G761(S) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HE84G761B | 制造商:KB 制造商全稱:KB 功能描述:8-BIT MICRO-CONTROLLER |

| HE84G762(S) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HE84G762B | 制造商:KB 制造商全稱:KB 功能描述:8-BIT MICRO-CONTROLLER |

| HE84G763(S) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。