- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384403 > HFA3841 (Intersil Corporation) 288 MACROCELL 3.3 VOLT ISP CPLD PDF資料下載

參數(shù)資料

| 型號: | HFA3841 |

| 廠商: | Intersil Corporation |

| 英文描述: | 288 MACROCELL 3.3 VOLT ISP CPLD |

| 中文描述: | 無線局域網(wǎng)媒體訪問控制器 |

| 文件頁數(shù): | 19/27頁 |

| 文件大?。?/td> | 211K |

| 代理商: | HFA3841 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

19

Buffer Access Paths

The HFA3841 has two independent buffer access paths,

which permits concurrent read and write transfers. The

firmware provides dynamic memory allocation between

Transmit and Receive, allowing efficient memory utilization.

On-the-fly allocation of (128-byte) memory blocks as needed

for reception wastes minimal space when receiving

fragments. The HFA3841 hides management of free

memory from the driver, and allows fast response and

minimum data copying for low latency. The firmware

provides direct access to TX and RX buffers based on

Frame ID (FID). This facilitates Power Management queuing,

and allows dynamic fragmentation and defragmentation by

controller. Simple Allocate/Deallocate commands insure low

host CPU overhead for memory management.

Hardware buffer chaining provides high performance while

reading and writing buffers. Data is transferred between the

host driver and the HFA3841 by writing or reading a single

register location (The Buffer Access Path, or BAP). Each

access increments the address in the buffer memory.

Internally, the firmware allocates blocks of memory as

needed to provide the requested buffer size. These blocks

may not be contiguous, but the firmware builds a linked list of

pointers between them. When the host driver is transferring

data through a buffer access path and reaches the end of a

physical memory block, hardware in the host interface

follows the linked list so that the buffer access path points to

the beginning of the next memory block. This process is

completely transparent to the host driver, which simply

writes or reads all buffer data to the same register. If the host

driver attempts to access beyond the end of the allocated

buffer, subsequent writes are ignored, and reads will be

undefined.

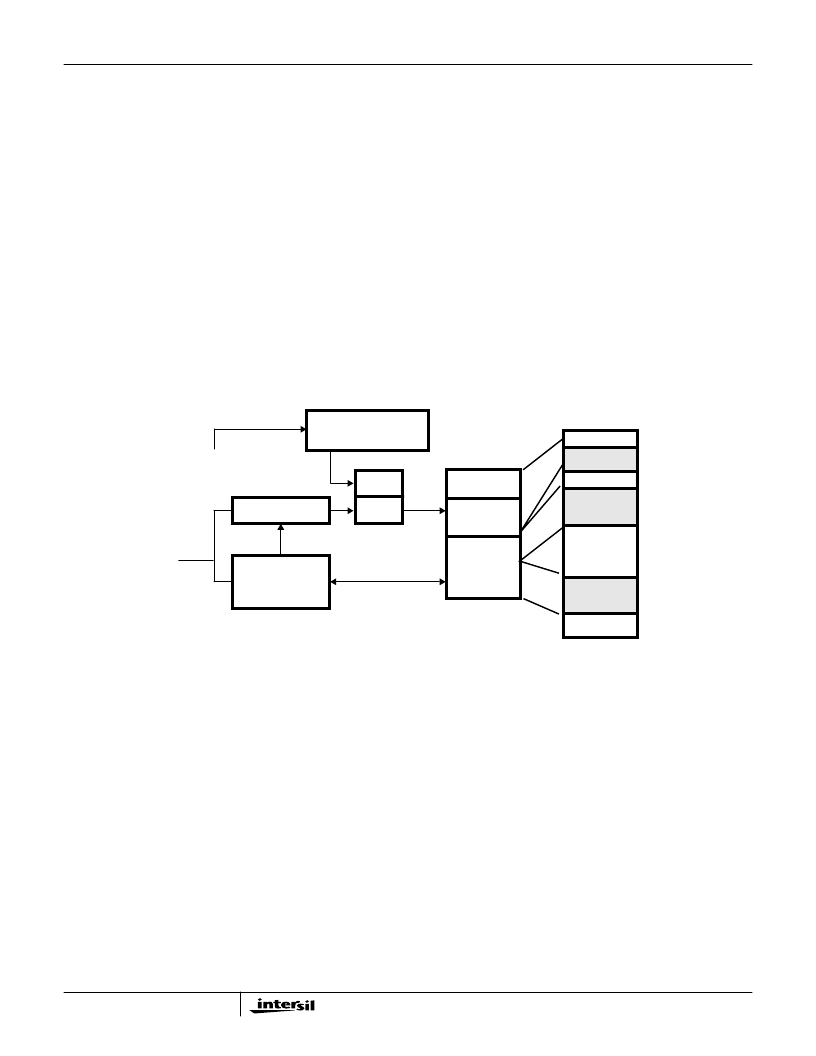

FIGURE 15. BLOCK DIAGRAM OF A BUFFER ACCESS PATH

BUFFER DESCRIPTOR

ACCESS (FIRMWARE)

ALLOCATE/

DEALLOCATE

REQUEST

BLOCK

OFFSET

VIRTUAL

FRAME BUFFER

DATA PORT

PRE-READ/

POST-WRITE

OFFSET CENTER

HOST

BUS

STATUS

HEADER

DATA

BUFFER

MEMORY

A

FID

D

Preliminary - HFA3841

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HFA3841CN | 288 MACROCELL 3.3 VOLT ISP CPLD |

| HFA3841CN96 | Wireless LAN Medium Access Controller |

| HFA3842A | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842AIN | 3.3V 288-mc CPLD |

| HFA3842AIN-TK | Circular Connector; No. of Contacts:41; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:20; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:20-41 RoHS Compliant: No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3841CN | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3841CN96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Medium Access Controller |

| HFA3842 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Medium Access Controller |

| HFA3842A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842AIN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:PCMCIA/USB Wireless LAN Medium Access Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。