- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384403 > HFA3841CN (INTERSIL CORP) 288 MACROCELL 3.3 VOLT ISP CPLD PDF資料下載

參數(shù)資料

| 型號: | HFA3841CN |

| 廠商: | INTERSIL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 288 MACROCELL 3.3 VOLT ISP CPLD |

| 中文描述: | 1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PQFP128 |

| 封裝: | PLASTIC, MS-026BHB, LQFP-128 |

| 文件頁數(shù): | 23/27頁 |

| 文件大?。?/td> | 211K |

| 代理商: | HFA3841CN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁

23

BBP Packet Transmission

There are 4 signals associated with the BBP Transmit Port:

TX_PE (transmit enable), TXRDY (transmit ready), TXD

(transmit data), and TXCLK (transmit clock). These connect

to the HFA3841 on PL0, PL7, TXD, and TXC, respectively.

State machines within the BBP control packet transmission

and reception. In the case of a transmission, the MAC

signals the BBP with the signal TX_PE. The BBP forms the

preamble and header and then signals the MAC to begin

transferring data with the signal TXRDY. This sequence is

illustrated in Figure 22 with detailed signal timing shown in

Figure 23 and specified delays contained in Table 3. Note

that if the MAC deactivates TX_PE too early it may cut off

modulation of the final symbol. For this reason, when

TX_PE is de-asserted the BBP will hold TXRDY active until

the last symbol containing data is modulated. This is

important for power sequencing and is discussed in more

detail in that section.

For more detailed information concerning BBP packet

transmission see the HFA3861 data sheet.

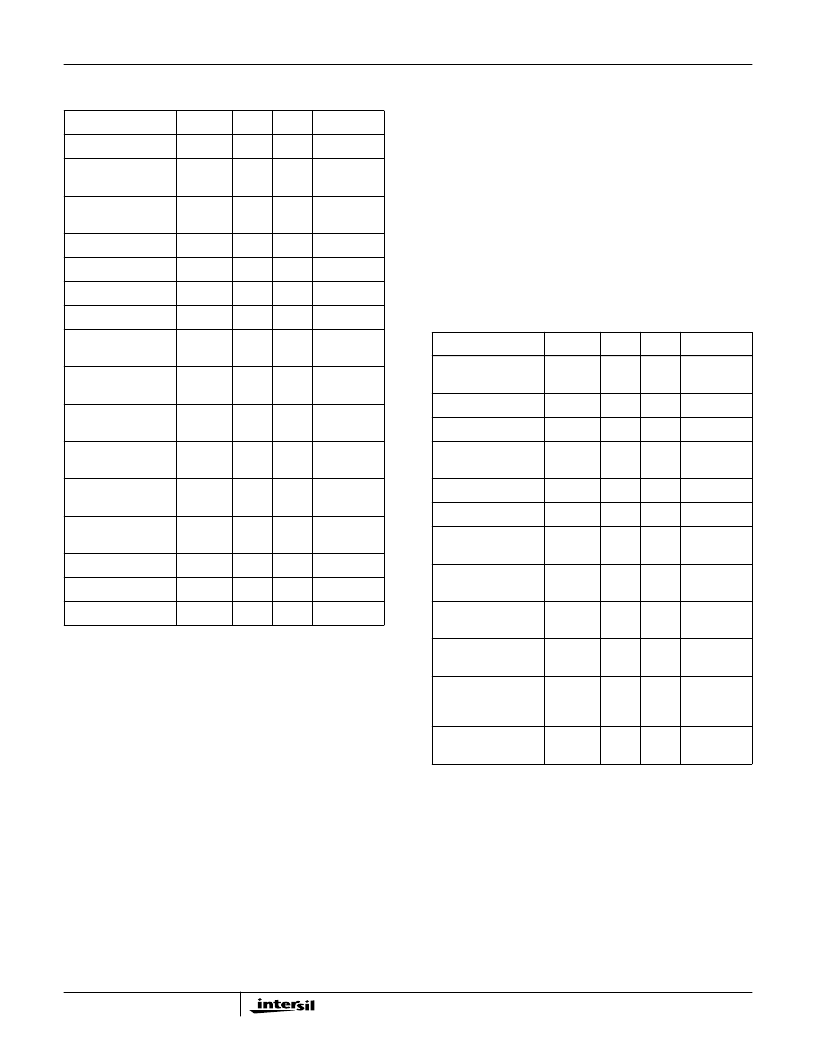

TABLE 2. BBP RECEIVE PORT AC ELECTRICAL

SPECIFICATIONS

PARAMETER

SYMBOL

MIN

MAX

UNITS

RX_PE Inactive Width

t

RLP

70

-

ns (Note 13)

RXC Period (11MBps

Mode)

t

RCP

77

-

ns

RXC Width Hi or Low

(11MBps Mode)

t

RCD

31

-

ns

RXC to RXD

t

RDD

20

60

ns

MD_RDY to 1st RXC

t

RD1

940

-

ns (Note 14)

RXD to 1st RXC

t

RD!

940

-

ns

Setup RXD to RXC

t

RDS

31

-

ns

RXC to RX_PE

Inactive (1MBps)

t

REH

0

925

ns (Note 15)

RXC to RX_PE

Inactive (2MBps)

t

REH

0

380

ns (Note 15)

RXC to RX_PE

Inactive (5.5MBps)

t

REH

0

140

ns (Note 15)

RXC to RX_PE

Inactive (11MBps)

t

REH

0

50

ns (Note 15)

RX_PE inactive to

MD_RDY Inactive

t

RD2

5

30

ns (Note 16)

Last Chip of SFD in to

MD_RDY Active

t

RD3

2.77

2.86

μ

s (Note 14)

RX Delay

2.77

2.86

μ

s (Note 17)

RX_PE to CCA Valid

t

CCA

-

10

μ

s (Note 18)

RX_PE to RSSI Valid

t

CCA

-

10

μ

s (Note 18)

NOTES:

13. RX_PE must be inactive at least 3 MCLKs before going active to

start a new CCA or acquisition.

14. MD_RDY programmed to go active after SFD detect (measured

from I

IN

, Q

IN

).

15. RX_PE active to inactive delay to prevent next RXC.

16. Assumes RX_PE inactive after last RXC.

17. MD_RDY programmed to go active at MPDU start. Measured

from first chip of first MPDU symbol at I

IN

, Q

IN

to MD_RDY

active.

18. CCA and RSSI are measured once during the first 10

μ

s interval

following RX_PE going active. RX_PE must be pulsed to initiate

a new measurement. RSSI may be read via serial port or from

Test Bus.

TABLE 3. BBP TRANSMIT PORT AC ELECTRICAL

SPECIFICATIONS

PARAMETER

SYMBOL

MIN

MAX

UNITS

TX_PE to I

OUT

/Q

OUT

(1st Valid Chip)

t

D1

2.18

2.3

μ

s (Note 19)

TX_PE Inactive Width

t

TLP

2.22

-

μ

s (Note 20)

TXC Width Hi or Low

t

TCD

40

-

ns

TXRDY Active to 1st

TX_CLK Hi

t

RC

260

-

ns

Setup TXD to TXC Hi

t

TDS

30

-

ns

Hold TXD to TXC Hi

t

TDH

0

-

ns

TXC to TX_PE

Inactive (1MBps)

t

PEH

0

965

ns (Note 22)

TXC to TX_PE

Inactive (2MBps)

t

PEH

0

420

ns (Note 22)

TXC to TX_PE

Inactive (5.5MBps)

t

PEH

0

160

ns (Note 22)

TXC to TX_PE

Inactive (11MBps)

t

PEH

0

65

ns (Note 22)

TXRDY Inactive To

Last Chip of MPDU

Out

t

RI

-20

20

ns

TXD Modulation

Extension

t

ME

2

-

μ

s (Note 21)

NOTES:

19. I

OUT

/Q

OUT

are modulated before first valid chip of preamble is

output to provide ramp up time for RF/IF circuits.

20. TX_PE must be inactive before going active to generate a new

packet.

21. I

OUT

/Q

OUT

are modulated after last chip of valid data to provide

ramp down time for RF/IF circuits.

22. Delay from TXC to inactive edge of TXPE to prevent next TXC.

BecauseTXPEasynchronouslystopsTXC,TXPEgoinginactive

within 40ns of TXC will cause TXC minimum hi time to be less

than 40ns.

Preliminary - HFA3841

相關PDF資料 |

PDF描述 |

|---|---|

| HFA3841CN96 | Wireless LAN Medium Access Controller |

| HFA3842A | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842AIN | 3.3V 288-mc CPLD |

| HFA3842AIN-TK | Circular Connector; No. of Contacts:41; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:20; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:20-41 RoHS Compliant: No |

| HFA3860B | Direct Sequence Spread Spectrum Baseband Processor(直接序列擴頻基帶處理器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3841CN96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Medium Access Controller |

| HFA3842 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Medium Access Controller |

| HFA3842A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842AIN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842AIN-TK | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:PCMCIA/USB Wireless LAN Medium Access Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復。