- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384403 > HFA3841CN (INTERSIL CORP) 288 MACROCELL 3.3 VOLT ISP CPLD PDF資料下載

參數(shù)資料

| 型號: | HFA3841CN |

| 廠商: | INTERSIL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 288 MACROCELL 3.3 VOLT ISP CPLD |

| 中文描述: | 1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PQFP128 |

| 封裝: | PLASTIC, MS-026BHB, LQFP-128 |

| 文件頁數(shù): | 9/27頁 |

| 文件大小: | 211K |

| 代理商: | HFA3841CN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

9

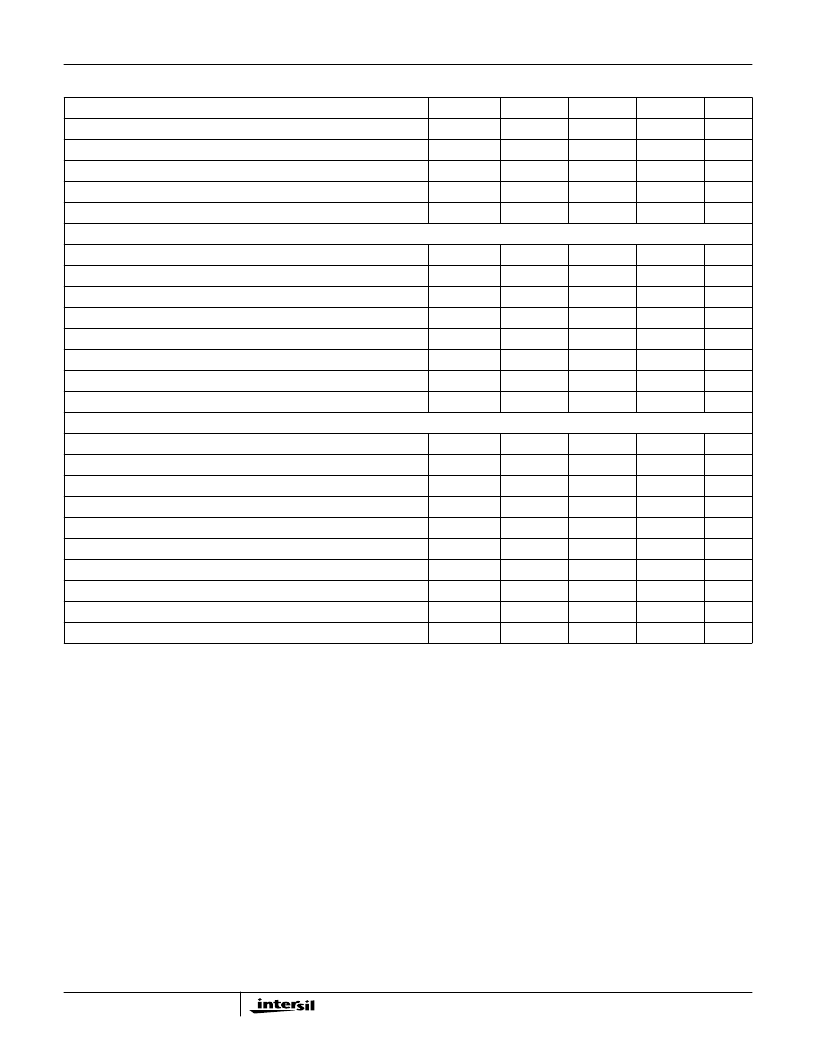

SIOIS16N Delay Falling from Address

t

DFIOIS16

-

-

35

ns

SIOIS16N Delay Rising from Address

t

DRIOIS16

-

-

35

ns

SWAITN Delay Falling from IOWRN

t

DFWT

-

-

35

ns

SWAITN Width Time

t

WWT

-

-

12,000

ns

SIOWRN High from SWAITN High

t

DRIOWR

0

-

-

ns

RADIO TX DATA - TX PATH

TXC Rising to TXD

t

DTXD

-

-

10

ns

TXC Period

t

TXC

4* t

TMCK

-

-

ns

TXC Width Hi

t

CHM

31

-

-

ns

TXC Width Lo

t

CLM

31

-

-

ns

MCLK Period

t

tMCK

22.7

-

-

ns

TXC Rising to TX_PE2 Deassert (See Note 9)

t

DTX_PE2

-

TBD

TBD

ns

TX_RDY Assert Before TXC Rising

t

TX_RDY

10

-

-

ns

TX_RDY Hold After TXC Rising (See Note 2)

t

TX_RDYH

0

-

-

RADIO RX DATA - RX PATH

RX_RDY Setup Time to RXC Positive Edge (See Note 3)

t

SURX_RDY

10

-

-

ns

RX_RDY Hold Time from RXC Positive Edge (See Note 4)

t

HRX_RDY

45

-

-

ns

RX_PE2 Delay from RX_RDY deAssert (See Note 8)

t

DRX_PE2

-

3 * t

MCLK

-

ns

RX_PE2 Low Pulse Width (See Note 7)

t

WRX_PE2

-

4 * t

MCLK

-

ns

RXD Setup Time to RXC Positive Edge (See Note 5)

t

SURXD

10

-

-

ns

RXD Hold Time from RXC Positive Edge (See Note 5)

t

HRXD

0

-

-

ns

RXC Period (See Note 9)

t

RXC

-

3 * t

MCLK

-

ns

MCLK Period

t

MCLK

22.7

-

-

ns

RXC Width Hi

t

RCHM

31

-

-

ns

RXC Width Lo

t

RCLM

31

-

-

ns

NOTES:

2. TX_RDY is and'd with TXC_ONE_SHOT to shift data in shift register. However, once the last data bit is put on TXD output pin no further shifting

of bits is required. In addition, TX_RDY remains asserted until TX_PE2 is de-asserted which occurs several MAC MCLK's after the last data bit

is shifted into the BBP TX_PORT. Therefore, 0ns hold time is required for this signal.

TX_RDY is used by the BBP to signal that the PLCP header and preamble have been generated and the MAC must provide the MPDU data.

TX_RDY will remain asserted until TX_PE2 is deasserted by the MAC.

TX_PE2 is async to the TX_PORT.

3. MD_RDY is and'd with RXC_ONE_SHOT (RXDAV) to shift data in shift register. RX_RDY is not required to be valid until 1 MCLK after RXC is

sampled high. Therefore, a negative setup time could be used. Since this is an unlikely scenario, we will leave it at a nominal 10ns setup time.

4. MD_RDY is and'd with RXC_ONE_SHOT (RXDAV) to shift data in shift register. Therefore, for the last data bit, the MD_RDY must be held active

until RXC_ONE_SHOT is sampled high by MAC's MCLK. However, it is assumed that BBP will be used in a mode that keeps RX_RDY

(MD_RDY) and RXC running until RX_PE2 is de-asserted. The MAC will stop processing data after the number of bits retrieved from the PLCP

header length field are received. THEREFORE, the RX_RDY hold time with respect to RXC does not matter. However, should the RX_RDY

signal be cleared when the last RXD bit is received the hold time w/r RXC must be honored.

5. RXC positive edge clocks a flop which stores the RXD for internal usage.

6. RXC period (and Hi/Lo times) must be long enough for flops clocked by MAC MCLK to see 1 RXC high and 1 RXC low. Since RXC can be async

to MAC MCLK it is assumed that 3 MCLK periods will suffice.

7. RX_PE inactive width at BBP is 3 BBP MCLK's. Since BBP MCLK and MAC MCLK can be async minimum should be 4 MAC MCLK's.

8. Not yet verified, but seems reasonable. When RX_RDY drops before expected number of RXD bits is received, then Tx/Rx FSM in mpctl.v

signals timers which clear rx_pe2_int. More of a functional spec than a timing spec.

9. Need to sample 1 RXC high and 1 RXC low with MAC MCLK.

AC Electrical Specifications

(Continued)

PARAMETER

SYMBOL

MIN

TYP

MAX

UNITS

Preliminary - HFA3841

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HFA3841CN96 | Wireless LAN Medium Access Controller |

| HFA3842A | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842AIN | 3.3V 288-mc CPLD |

| HFA3842AIN-TK | Circular Connector; No. of Contacts:41; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:20; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:20-41 RoHS Compliant: No |

| HFA3860B | Direct Sequence Spread Spectrum Baseband Processor(直接序列擴頻基帶處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3841CN96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Medium Access Controller |

| HFA3842 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Medium Access Controller |

| HFA3842A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842AIN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842AIN-TK | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:PCMCIA/USB Wireless LAN Medium Access Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復。