- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384423 > HIP7010P (HARRIS SEMICONDUCTOR) FPGA 2000000 SYSTEM GATE 1.8 VOLT - NOT RECOMMENDED for NEW DESIGN PDF資料下載

參數(shù)資料

| 型號: | HIP7010P |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 網(wǎng)絡接口 |

| 英文描述: | FPGA 2000000 SYSTEM GATE 1.8 VOLT - NOT RECOMMENDED for NEW DESIGN |

| 中文描述: | DATACOM, INTERFACE CIRCUIT, PDIP14 |

| 文件頁數(shù): | 9/20頁 |

| 文件大小: | 106K |

| 代理商: | HIP7010P |

9

Bus Arbitration

The nature of multiplexed communications leads to contention

issues when two or more nodes attempt to transmit on the bus

simultaneously. Within J1850 VPW systems, messages are

assigned varying levels of priority which allows implementa-

tion of an arbitration scheme to resolve potential contentions.

The specified arbitration is performed on a symbol by symbol

basis throughout the duration of every message.

Arbitration begins with the rising edge of the SOF pulse. No

node should attempt to issue an SOF until an Idle bus has

been detected (i.e., an Inter-Frame Separation (IFS)symbol

with a period of TV6 has been received). If multiple nodes are

ready to access the bus and are all waiting for an IFS to

elapse, invariable skews in timing components will cause one

arbitrary node to detect the Idle condition before all others and

start transmission first. For this reason, all nodes waiting for

an IFS will consider an IFS to have occurred if either:

1. An IFS nominal period has elapsed

or

2. An EOF minimum period has elapsed anda rising edge

has been detected

Arbitrating devices will all be synchronized during the SOF.

Beginning with the first data bit and continuing to the EOF,

every transmitting device is responsible for verifying that the

symbol it sent was the symbol which appeared on the bus.

Each transition, every transmitting node must decode the

symbol, verify the received symbol matches the one sent, and

begin timing of the next symbol. Since timing of the next sym-

bol begins with the last transition detected on the bus, all

transmitters are re-synchronized each symbol. When the

received symbol doesn’t match the symbol sent, a conflict (bit

collision) occurs. Any device detecting a collision will assume

it has lost arbitration and immediately relinquish the bus. Typi-

cally, after losing arbitration, a device will attempt retransmis-

sion of the message when the bus once again becomes idle.

The definition of 1 and 0 data bits (see Table 2 and discussion

under

VPW Symbol Definitions

) leads to 0’s having priority

over 1’s in this arbitration scheme. Header bytes are generally

assigned such that arbitration is completed before the first

data byte is transmitted. Because of the dominance of 0 bits

and the MSB first bit order, a header with the hexadecimal

value $00 will have highest priority, then $01, $02, $03, etc.

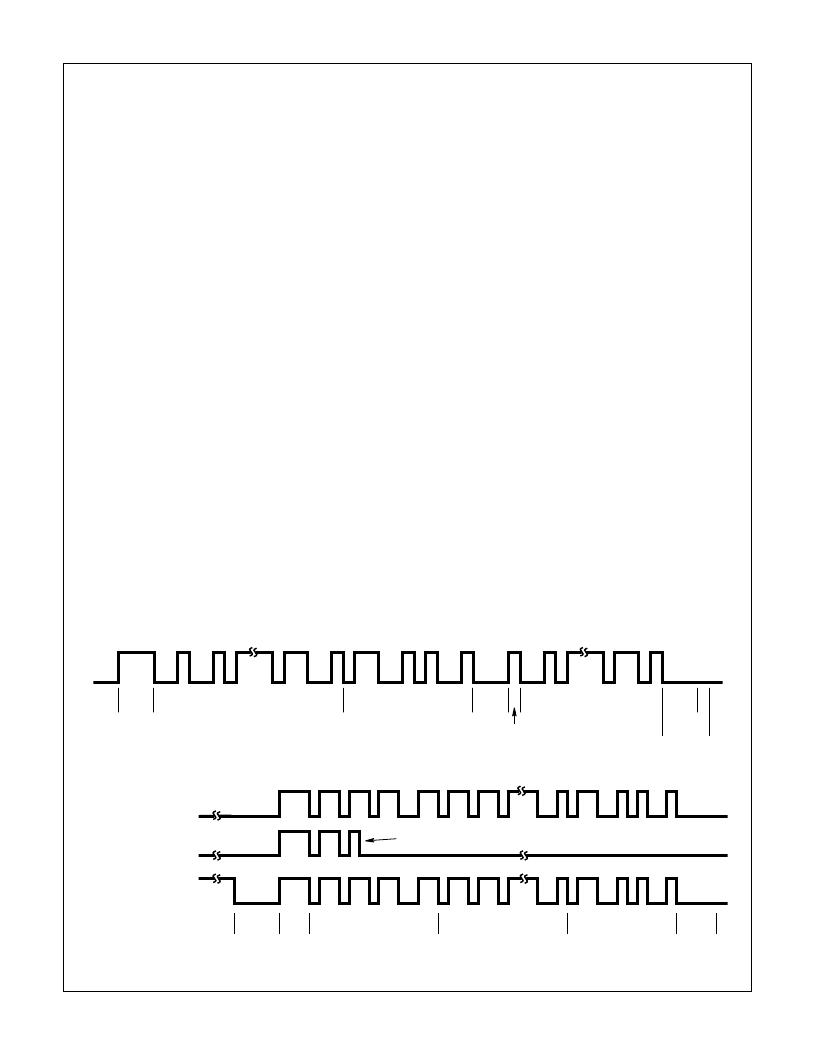

An example of two nodes arbitrating for control of the bus is

shown in Figure 6.

Arbitration also takes place during the IFR portion of a mes-

sage, if more than one node is attempting to generate a

response. Arbitration begins with the NB symbol, which fol-

lows the EOD and precedes the first IFR byte.

For Type 1 and Type 3 messages only, the respondent which

successfully arbitrates for control of the bus produces an IFR.

All other respondents abort their IFRs.

For Type 2 messages, all respondents which lose arbitration

must re-attempt transmission at the end of each byte. Each

node, which successfully responds, eliminates itself from the

subsequent arbitration until all nodes have responded. This

arbitration scheme limits each respondent to a single byte dur-

ing a Type 2 IFR.

Break

To force a message to be aborted before EOF is reached, a

break (BRK) symbol can be transmitted by any node. The

BRK symbol is an active pulse of duration TV5. Reception of a

break causes all nodes to reset to a ready-to-receivestate

and to re-arbitrate for control following an IFS.

HIP7010 Architectural Overview

The HIP7010 consists of three major functional blocks: the

Serial Interface System (SERIAL) block; the State Machine

(STATE) block; and the Symbol Encoder/Decoder (SENDEC)

block. Transfers between the Host and the HIP7010 are con-

trolled by the SERIAL block, while transfers between the

J1850 bus and the HIP7010 are handled by the SENDEC

FIGURE 5. J1850 MESSAGE WITH IN-FRAME-RESPONSE

FIGURE 6. TWO NODES ARBITRATING FOR CONTROL OF J1850 BUS

SOF

HEADER

. . . . DATA N

CRC

IN FRAME RESPONSE

EOD

NB

EOD

EOF

SOF

0

0

0

0

0

0

0

1

1

0

0

HEADER

COLLISION DETECTED BY B

J1850

TRANSMITTER

B

TRANSMITTER

A

DATA 1 . . . DATA N

CRC

EOF

IFS

BUS

HIP7010

相關PDF資料 |

PDF描述 |

|---|---|

| HIP7020 | FPGA 2000000 SYSTEM GATE 1.8 VOLT - NOT RECOMMENDED for NEW DESIGN |

| HIP7020AB | FPGA 2000000 SYSTEM GATE 1.8 VOLT - NOT RECOMMENDED for NEW DESIGN |

| HIP7020AP | FPGA 2000000 SYSTEM GATE 1.8 VOLT - NOT RECOMMENDED for NEW DESIGN |

| HIP7030A0 | J1850 8-Bit 68HC05 Microcontroller Emulator Version |

| HIP7030A0M | FPGA - 200000 SYSTEM GATE 2.5 VOLT - NOT RECOMMENDED for NEW DESIGN |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HIP7010P WAF | 制造商:Harris Corporation 功能描述: |

| HIP7020 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:J1850 Bus Transceiver For Multiplex Wiring Systems |

| HIP7020 DIE | 制造商:Harris Corporation 功能描述: |

| HIP7020AB | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:J1850 Bus Transceiver For Multiplex Wiring Systems |

| HIP7020AP | 制造商:Harris Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。