- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379204 > IBM13M32734JCA (IBM Microeletronics) 32M x 72 Two Bank Registered/Buffered SDRAM Module(64M x 64 2組不帶緩沖同步動態(tài)RAM模塊) PDF資料下載

參數(shù)資料

| 型號: | IBM13M32734JCA |

| 廠商: | IBM Microeletronics |

| 英文描述: | 32M x 72 Two Bank Registered/Buffered SDRAM Module(64M x 64 2組不帶緩沖同步動態(tài)RAM模塊) |

| 中文描述: | 32M × 72配置兩個銀行的注冊/緩沖內(nèi)存模組(64米× 64 2組不帶緩沖同步動態(tài)內(nèi)存模塊) |

| 文件頁數(shù): | 17/20頁 |

| 文件大小: | 529K |

| 代理商: | IBM13M32734JCA |

IBM13M32734JCA

32M x 72 Two Bank Registered/Buffered SDRAM Module

09K3883.F38743

4/00

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 17 of 20

Functional Description and Timing Diagrams

Refer to the IBM 128Mb Synchronous DRAM Die Revision A datasheet (Document 33L8019) for the func-

tional description and timing diagrams for buffered-mode operation.

Refer to the IBM Application Notes Serial Presence Detect on Memory DIMMsand SDRAM Presence Detect

Definitions for the Serial Presence Detect functional description and timings.

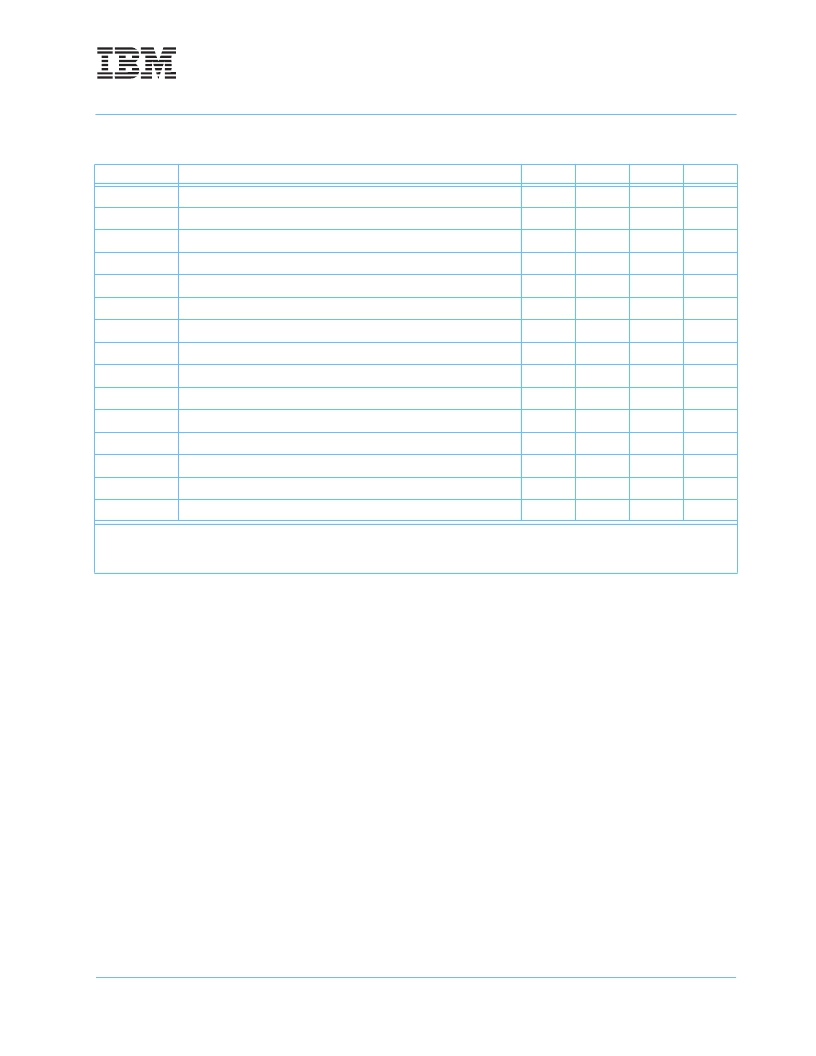

Presence Detect Read and Write Cycle

Symbol

Parameter

Min.

Max.

Units

Notes

f

SCL

SCL Clock Frequency

—

100

KHz

T

I

Noise Suppression Time Constant at SCL, SDA Inputs

—

100

ns

t

AA

SCL Low to SDA Data Out Valid

0.3

3.5

μ

s

t

BUF

Time the Bus Must Be Free before a New Transmission Can Start

4.7

—

μ

s

t

HD:STA

Start Condition Hold Time

4.0

—

μ

s

t

LOW

Clock Low Period

4.7

—

μ

s

t

HIGH

Clock High Period

4.0

—

μ

s

t

SU:STA

Start Condition Setup Time (for a Repeated Start Condition)

4.7

—

μ

s

t

HD:DAT

Data in Hold Time

0

—

μ

s

t

SU:DAT

Data in Setup Time

250

—

ns

t

R

SDA and SCL Rise Time

—

1

μ

s

t

F

SDA and SCL Fall Time

—

300

ns

t

SU:STO

Stop Condition Setup Time

4.7

—

μ

s

t

DH

Data Out Hold Time

300

—

ns

t

WR

Write Cycle Time

—

15

ms

1

1. The write cycle time (t

WR

) is the time from a valid stop condition of a write sequence to the end of the internal erase/program cycle.

During the write cycle, the bus interface circuits are disabled, SDA is allowed to remain high per the bus-level pull-up resistor, and

the device does not respond to its slave address.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM13M64734BCA | 64M x 72 1 Bank Registered/Buffered SDRAM Module(64M x 72 1組寄存/緩沖同步動態(tài)RAM模塊) |

| IBM13M64734CCA | 64M x 72 2-Bank Registered/Buffered SDRAM Module(64M x 72 2組寄存/緩沖同步動態(tài)RAM模塊) |

| IBM13M64734HCA | 64M x 72 Two-Bank Registered SDRAM Module(64M x 72 2組帶寄存同步動態(tài)RAM模塊) |

| IBM13M8734HCB | 8M x 72 1 Bank Registered SDRAM Module with PLL(8M x 72 1組帶鎖相環(huán)的寄存同步動態(tài)RAM模塊) |

| IBM13M8734HCC | 8M x 72 1 Bank Registered/Buffered SDRAM Module(8M x 72 1組寄存/緩沖同步動態(tài)RAM模塊) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM14H5481 | 制造商:AVED Memory Products 功能描述: |

| IBM14H5540 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM17R8251 | 制造商:AVED Memory Products 功能描述: |

| IBM17R8252 | 制造商:AVED Memory Products 功能描述: |

| IBM1805T | 制造商:Schneider Electric 功能描述:IBM1805T |

發(fā)布緊急采購,3分鐘左右您將得到回復。