- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379205 > IBM13T2649NC (IBM Microeletronics) 2M x 64 SDRAM SO DIMM(2M x 64小外形雙列直插同步動(dòng)態(tài)RAM模塊) PDF資料下載

參數(shù)資料

| 型號(hào): | IBM13T2649NC |

| 廠商: | IBM Microeletronics |

| 英文描述: | 2M x 64 SDRAM SO DIMM(2M x 64小外形雙列直插同步動(dòng)態(tài)RAM模塊) |

| 中文描述: | 200萬蘇× 64 SDRAM的內(nèi)存(2米× 64小外形雙列直插同步動(dòng)態(tài)內(nèi)存模塊) |

| 文件頁數(shù): | 8/15頁 |

| 文件大小: | 303K |

| 代理商: | IBM13T2649NC |

IBM13T2649NC

2M x 64 SDRAM SO DIMM

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 8 of 15

88H4961

GA14-4477-01

Rev 3/98

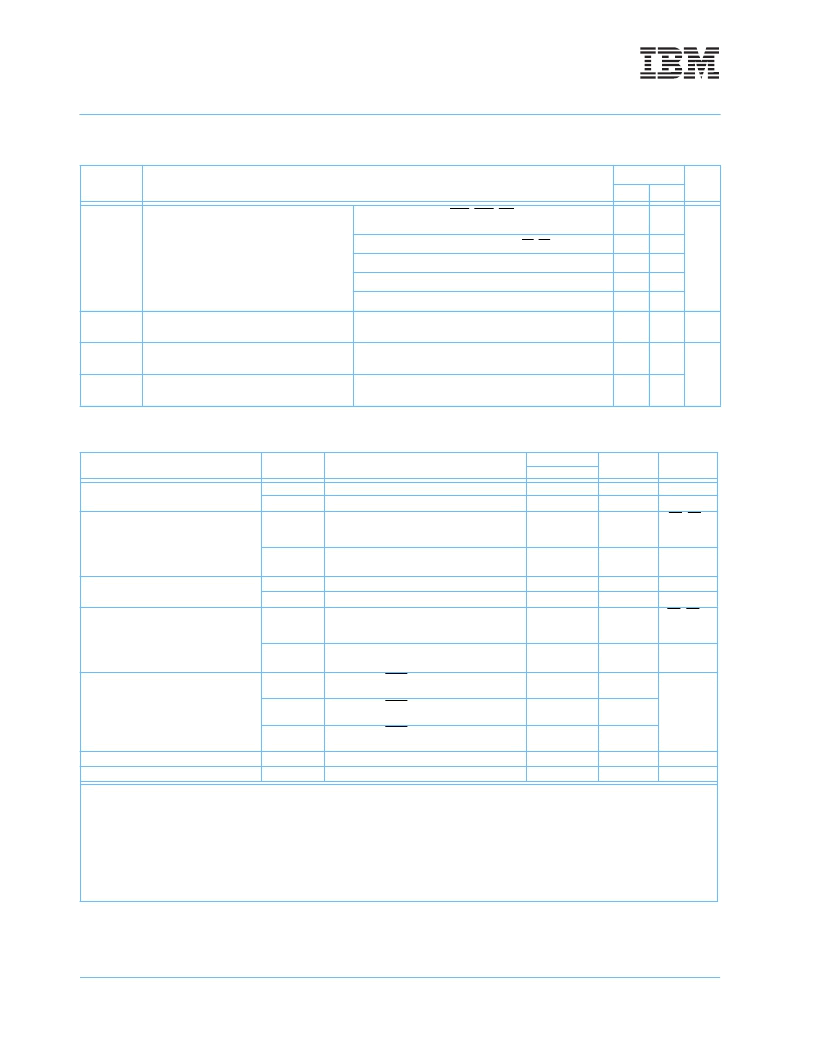

Output Characteristics

(T

A

= 0 to +70C, V

DD

= 3.3V

±

0.3V)

Symbol

Parameter

x64

Units

Min.

Max.

I

I(L)

Input Leakage Current, any input

(0.0V

≤

V

IN

≤

3.6V), All Other Pins

Not Under Test = 0V

RAS, CAS, WE,

A0-A9, A10/AP, BA0

-8

+8

μ

A

CK0, CK1, CKE0, CKE1, S0, S1

-4

+4

DQMB0 - 7

-1

+1

DQ0 - 63

-1

+1

SCL, SDA

-1

+1

I

O(L)

Output Leakage Current

(D

OUT

is disabled, 0.0V

≤

V

OUT

≤

3.6V)

DQ0 - 63, SDA

-1

+1

μ

A

V

OH

Output Level

Output “H” Level Voltage (I

OUT

= -2.0mA)

2.4

V

DD

V

V

OL

Output Level

Output “L” Level Voltage (I

OUT

= +2.0mA)

0.0

0.4

Standby and Refresh Currents

(T

A

= 0 to +70C, V

DD

= 3.3V

±

0.3V)

Parameter

Symbol

Test Condition

Organization

x64

24

16

Units

Notes

Precharge Standby Current in Power

Down Mode

I

DD

1

P

I

DD

1

PS

CKE0, 1

≤

V

IL

(max), t

CK

= 15ns

CKE0, 1

≤

V

IL

(max), t

CK

= Infinity

CKE0, 1

≥

V

IH

(min), t

CK

= 15ns

Input Change every 30ns

CKE0, 1

≥

V

IH

(min), t

CK

= Infinity

No Input Change

CKE0, 1

≤

V

IL

(max), t

CK

= 15ns

CKE0, 1

≤

V

IL

(max), t

CK

= Infinity

CKE0, 1

≥

V

IH

(min), t

CK

= 15ns

Input Change every 30ns

CKE0, 1

≥

V

IH

(min), t

CK

= Infinity

No Input Change

CAS Latency = 1

t

RC

≥

t

RC

(min)

CAS Latency = 2

t

RC

≥

t

RC

(min)

CAS Latency = 3

t

RC

≥

t

RC

(min)

CKE0, 1

≤

0.2V

V

IN

= GND or V

DD

mA

mA

1

1

Precharge Standby Current in Non-

Power Down Mode

I

DD

1

N

200

mA

S0, S1=

High

1

I

DD

1

NS

80

mA

1

Active Standby Current in Power

Down Mode

I

DD

2

P

I

DD

2

PS

24

16

mA

mA

1, 2

1, 2

Active Standby Current in Non-Power

Down Mode

I

DD

2

N

200

mA

S0, S1 =

High

1

I

DD

2

NS

120

mA

1

Auto (CBR) Refresh Current

I

DD

3

440

mA

3, 4, 5, 6

460

mA

540

mA

Self Refresh Current

Serial PD Device Standby Current

I

DD

4

I

DD

8

mA

μ

A

1

7

10

1. The specified values are for both SO DIMM banks operating in the specified mode.

2. Active Standby Current will be higher if Clock Suspend is entered during a Burst Read Cycle (add 1mA per DQ).

3. The specified values are valid when addresses are changed no more than once during t

CK

(min).

4. The specified values are valid when No Operation commands are registered on every rising clock edge during t

RC

(min).

5. The specified values are valid when data inputs (DQ’s) are stable during t

RC

(min).

6. The specified values are valid when one SO DIMM bank is Auto (CBR) Refresh and the other SO DIMM bank is in Active Standby

(I

DD

2

N).

7. V

DD

= 3.3V

Discontinued (12/98 - last order; 9/99 last ship)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM13T4644MC | 1M x 64 SDRAM SO DIMM(1M x 64 同步動(dòng)態(tài)RAM模塊) |

| IBM13T1649NC | 1M x 64 SDRAM SO DIMM(1M x 64 同步動(dòng)態(tài)RAM模塊) |

| IBM13T4644MPC | 4M x 64 SDRAM SO DIMM(Small Outline Dual In-line Memory Module)(4M x 64小外形雙列直插同步動(dòng)態(tài)RAM模塊) |

| IBM13T4644MPD | One Bank 4M x 64 SDRAM SO DIMM(Small Outline Dual In-line Memory Module)(1組 4M x 64 PC100小外形雙列直插同步動(dòng)態(tài)RAM模塊) |

| IBM13T4644MPE | 4M x 64 PC100 SDRAM SO DIMM(Small Outline Dual In-line Memory Module)(4M x 64 PC100小外形雙列直插式同步動(dòng)態(tài)RAM模塊) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM14H5481 | 制造商:AVED Memory Products 功能描述: |

| IBM14H5540 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM17R8251 | 制造商:AVED Memory Products 功能描述: |

| IBM17R8252 | 制造商:AVED Memory Products 功能描述: |

| IBM1805T | 制造商:Schneider Electric 功能描述:IBM1805T |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。