- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379205 > IBM3209K3114 (IBM Microeletronics) IBM Packet Routing Switch Serial Interface Converter(IBM封裝路線選擇開(kāi)關(guān)串行接口轉(zhuǎn)換器) PDF資料下載

參數(shù)資料

| 型號(hào): | IBM3209K3114 |

| 廠商: | IBM Microeletronics |

| 英文描述: | IBM Packet Routing Switch Serial Interface Converter(IBM封裝路線選擇開(kāi)關(guān)串行接口轉(zhuǎn)換器) |

| 中文描述: | IBM的分組路由交換機(jī)串行接口轉(zhuǎn)換器(IBM的封裝路線選擇開(kāi)關(guān)串行接口轉(zhuǎn)換器) |

| 文件頁(yè)數(shù): | 38/152頁(yè) |

| 文件大小: | 2390K |

| 代理商: | IBM3209K3114 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)

IBM3209K3114

IBM Packet Routing Switch Serial Interface Converter

Advance

Functional Description

Page 28 of 142

prssi.01

July 12, 2000

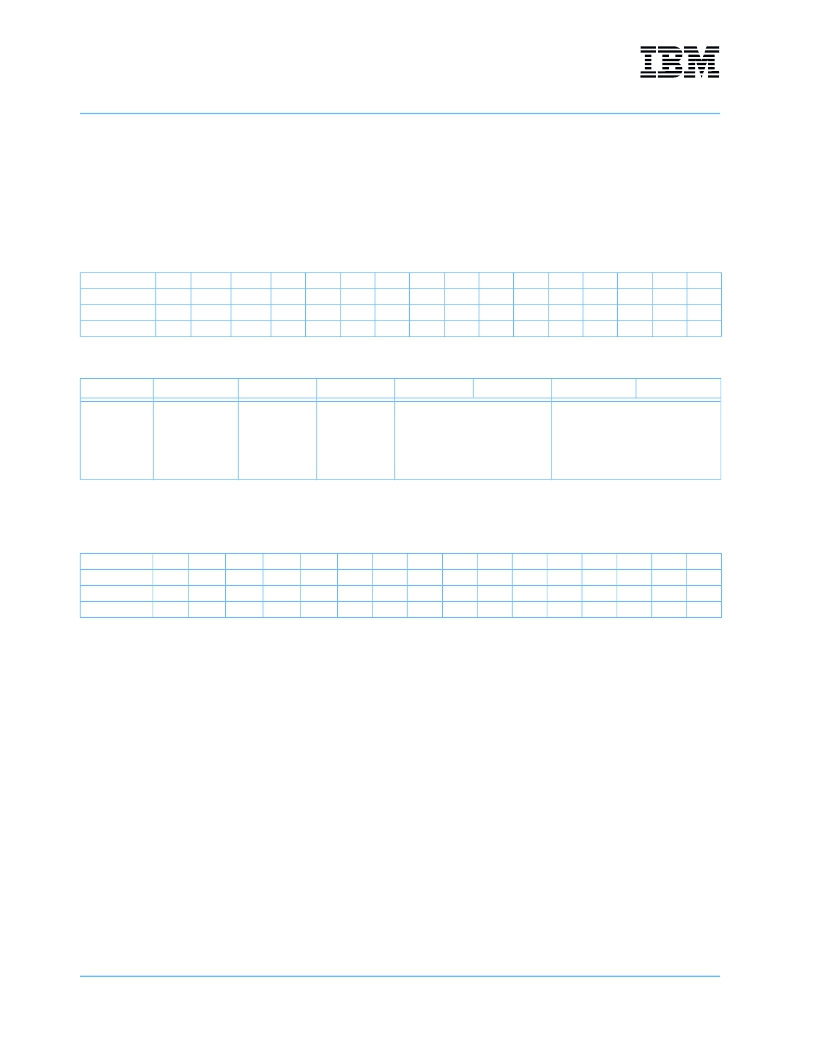

3.6.4.1 Packets Format

Idle Packets

Idle packets received from EDI have the following format:

16x16 Switch Interface

For idle packets PQ is mapped as follows:

Parity Bit is EVEN parity over 3 bytes PQ, OQG1 and OQG2

32x32 SWITCH Interface

In the packet qualifier the parity bit is EVEN parity over 5 bytes PQ, OQG1, OQG2, OQG3 and OQG4

Note:

The content of PQ byte for yellow packets received from the switch is

’

01001000

’

. It does not contain

flywheel synchronization information because it is generated by the switch control. In the switch, egress yel-

low packets are considered data packets and therefore do not contain link CRC information fields. Yellow

packets are detected and an interruption is reported when the detection function is enabled. When detection

is disabled, the yellow packet is considered a normal time fill packet (idle packet).

Idle Packet CRC Computing

Idle packet CRC detects physical media errors, so the 4x LUs must be covered. The last byte of each LU for

each idle packet carries a CRC byte protecting each LU. The four LU CRC bytes are cumulative between two

idle packets.

The CRC polynom is X8+X4+X3+X2+1. The CRC register is initialized (configuration table address 08 @ 28,

bits 24-31) depending on the LU depth.

Container

Master LU

Slave LU

Slave LU

Slave LU

C00

PQ

x

’

CC

’

x

’

CC

’

x

’

CC

’

C01

OQG1 OQG2

x

’

00

’

x

’

00

’

x

’

00

’

C02

C03

x

’

00

’

x

’

00

’

x

’

00

’

x

’

00

’

C04

x

’

00

’

x

’

00

’

x

’

00

’

x

’

00

’

C05

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

C06

C07

C08

C09

C10

C11

x

’

00

’

x

’

00

’

x

’

00

’

x

’

00

’

C12

x

’

00

’

x

’

00

’

x

’

00

’

x

’

00

’

C13

x

’

00

’

x

’

00

’

x

’

00

’

x

’

00

’

C14

x

’

00

’

x

’

00

’

x

’

00

’

x

’

00

’

C15

CRC

CRC

CRC

CRC

x

’

00

’

x

’

00

’

x

’

00

’

Bit_ 0

Bit_1

Bit_2

Bit_3

Bit_4

Bit_5

Bit_6

Bit_7

0

Header Parity

PQ OQG1

OQG2

0

0

00 (Blue Colored Packet)

01 (Red Colored Packet)

00

01

10

11

Flywheel Counter Synchronization

Highest Priority

Lowest Priority

Master LU

Slave LU

Slave LU

Slave LU

PQ

x

’

CC

’

x

’

CC

’

x

’

CC

’

OQG1 OQG2 OQG3 0QG4 x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

x

’

CC

’

CRC

CRC

CRC

CRC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM32NPCXX1EPABBE66 | IBM Processor for Network Resources(異步轉(zhuǎn)換模式(ATM)32位微處理器(用于網(wǎng)絡(luò)資源管理)) |

| IBM39MPEGCS24DPFA16C | High Performance Audio/Video Decoder(高性能音頻/視頻譯碼器) |

| IBM39MPEGCS24PFA16C | High Performance Audio/Video Decoder(高性能音頻/視頻譯碼器) |

| IBM39STB130x0 | STB130x0 A/V Transport/Decoders(STB130x0 音頻/視頻的傳送譯碼器) |

| IBM42F10SNNAA20 | SFF-1063/1250N-SW PTH Serial Optical Transceiver(SFF-1063/1250N-SW PTH串行光纖收發(fā)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM3209K4060 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecom Switching Circuit |

| IBM3288H2848 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| IBM32NPR100EXXCAB133 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| IBM32NPR101EPXCAC133 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| IBM35CPC945C03C-2 | 制造商:IBM 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。