- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379206 > IBMN312164CT3 (IBM Microeletronics) 128Mb(8Mbit x 4 I/O x 4 Bank) Synchronous DRAM(128M位(8M位 x 4 I/O x 4 組)同步動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | IBMN312164CT3 |

| 廠商: | IBM Microeletronics |

| 英文描述: | 128Mb(8Mbit x 4 I/O x 4 Bank) Synchronous DRAM(128M位(8M位 x 4 I/O x 4 組)同步動(dòng)態(tài)RAM) |

| 中文描述: | 128Mb的(8Mbit × 4的I / O × 4行)同步DRAM(128兆位(800萬位× 4的I / O × 4組)同步動(dòng)態(tài)RAM)的 |

| 文件頁(yè)數(shù): | 27/66頁(yè) |

| 文件大小: | 1696K |

| 代理商: | IBMN312164CT3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)

IBMN312164CT3

IBMN312804CT3

IBMN312404CT3

Preliminary

128Mb Synchronous DRAM - Die Revision B

06K7582.H03335A

10/00

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 27 of 66

Data Mask

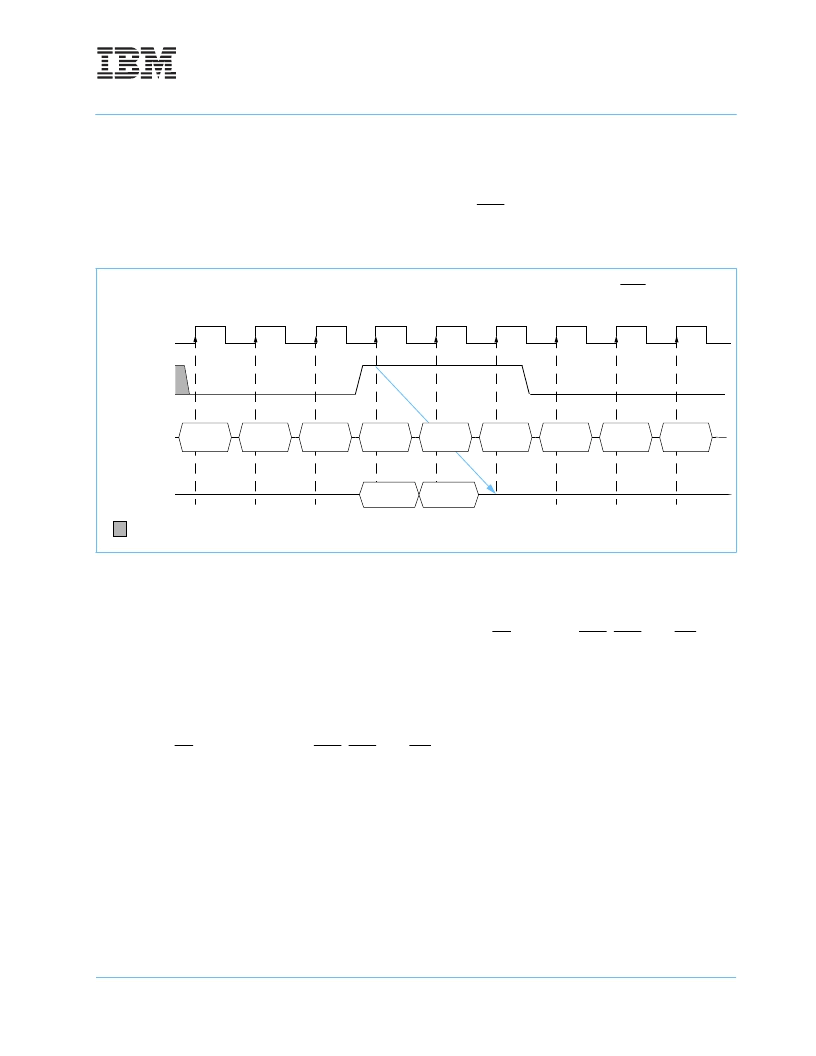

The SDRAM has a Data Mask function that can be used in conjunction with data read and write cycles. When

the Data Mask is activated (DQM high) during a write cycle, the write operation is prohibited immediately

(zero clock latency). If the Data Mask is activated during a read cycle, the data outputs are disabled and

become high impedance after a two-clock delay, independent of CAS latency.

No Operation Command

The No Operation Command should be used in cases when the SDRAM is in an idle or a wait state. The pur-

pose of the No Operation Command is to prevent the SDRAM from registering any unwanted commands

between operations. A No Operation Command is registered when CS is low with RAS, CAS, and WE held

high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is

still executing, such as a burst read or write cycle.

Deselect Command

The Deselect Command performs the same function as a No Operation Command. Deselect Command

occurs when CS is brought high, the RAS, CAS, and WE signals become don’t cares.

Data Mask Activated during a Read Cycle

COMMAND

NOP

READ A

NOP

NOP

NOP

NOP

NOP

NOP

NOP

DQM

: “H” or “L”

A two-clock delay before

the DQs become Hi-Z

DQs

CK

T0

T2

T1

T3

T4

T5

T6

T7

T8

DOUT A

0

DOUT A

1

(Burst Length = 4, CAS Latency = 2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBMN325404CT3 | 256Mb(4Mbit x 16 I/O x 4 Bank) Synchronous DRAM(256M位(4M位 x 16 I/O x 4 組)同步動(dòng)態(tài)RAM) |

| IBMN325804CT3 | 256Mb(8Mbit x 8 I/O x 4 Bank) Synchronous DRAM(256M位(8M位 x 8 I/O x 4 組)同步動(dòng)態(tài)RAM) |

| IBMN325164CT3 | 256Mb(16Mbit x 4 I/O x 4 Bank) Synchronous DRAM(256M位(16M位 x 4 I/O x 4 組)同步動(dòng)態(tài)RAM) |

| IBMN612404GT3B | 128Mb Double Data Rate Synchronous DRAM(128M位高速CMOS同步動(dòng)態(tài)RAM(采用雙數(shù)據(jù)速率結(jié)構(gòu))) |

| IBMN612804GT3B | 128Mb Double Data Rate Synchronous DRAM(128M位高速CMOS同步動(dòng)態(tài)RAM(采用雙數(shù)據(jù)速率結(jié)構(gòu))) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBMN364164CT3C360 | 制造商:IBM 功能描述:* |

| IBMPPC403GAJC33C1 | 制造商:IBM 功能描述: |

| IBMPPC750CLGEQ4023 | 制造商:IBM 功能描述:MPU 750CL RISC 32BIT 90NM 400MHZ 1.15V/1.8V 278FCBGA - Trays |

| IBMPPC750CLGEQ5023 | 制造商:IBM Microelectronics 功能描述:MPU 750CL RISC 32BIT 90NM 500MHZ 1.15V/1.8V 278FCBGA - Trays |

| IBMPPC750CLGEQA033 | 制造商:IBM 功能描述:MPU 750CL RISC 32BIT 90NM 1GHZ 1.15V/1.8V 278FCBGA - Trays 制造商:IBM 功能描述:IBMIBMPPC750CLGEQA033 CPU PPC 750CL 1GHZ |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。