- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379206 > IBMN612804GT3B (IBM Microeletronics) 128Mb Double Data Rate Synchronous DRAM(128M位高速CMOS同步動態(tài)RAM(采用雙數(shù)據(jù)速率結構)) PDF資料下載

參數(shù)資料

| 型號: | IBMN612804GT3B |

| 廠商: | IBM Microeletronics |

| 英文描述: | 128Mb Double Data Rate Synchronous DRAM(128M位高速CMOS同步動態(tài)RAM(采用雙數(shù)據(jù)速率結構)) |

| 中文描述: | 128Mb的雙數(shù)據(jù)速率同步DRAM(128兆位高速的CMOS同步動態(tài)隨機存儲器(采用雙數(shù)據(jù)速率結構)) |

| 文件頁數(shù): | 63/79頁 |

| 文件大?。?/td> | 1324K |

| 代理商: | IBMN612804GT3B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁當前第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁

IBMN612404GT3B

IBMN612804GT3B

Preliminary

128Mb Double Data Rate Synchronous DRAM

06K0566.F39350B

1/01

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 63 of 79

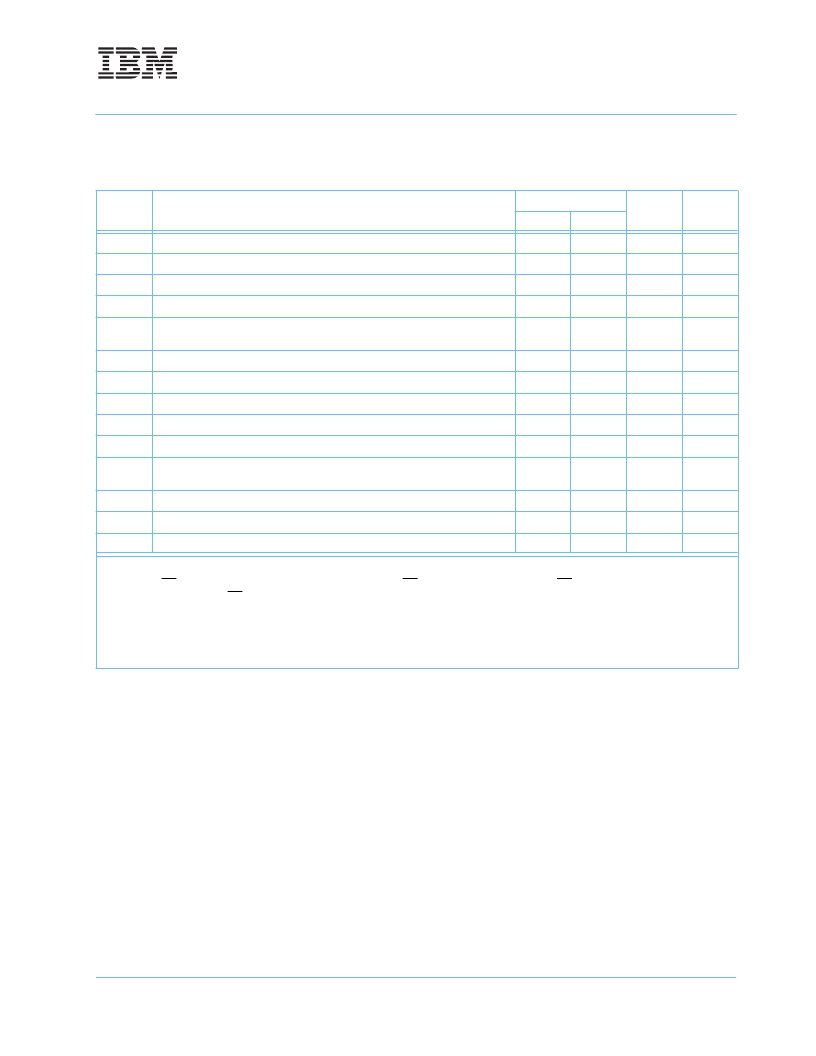

Electrical Characteristics & AC Timing for DDR266B - Applicable Specifications

Expressed in Clock Cycles

(0

°

C

≤

T

A

≤

70

°

C

;

V

DDQ

= 2.5V

±

0.2V; V

DD

= 2.5V

±

0.2V, See AC

Characteristics)

Symbol

Parameter

DDR266B @ CL = 2.5

Units

Notes

Min

Max

t

MRD

Mode register set command cycle time

2

t

CK

1, 2, 3, 4

t

WPRE

Write preamble

0.25

t

CK

1, 2, 3, 4

t

RAS

Active to Precharge command

6

16000

t

CK

1, 2, 3, 4

t

RC

Active to Active/Auto-refresh command period

9

t

CK

1, 2, 3, 4

t

RFC

Auto-refresh to Active/Auto-refresh

command period

10

t

CK

1, 2, 3, 4

t

RCD

Active to Read or Write delay

3

t

CK

1, 2, 3, 4

t

RAP

Active to Read Command with Autoprecharge

3

t

CK

1, 2, 3, 4

t

RP

Precharge command period

3

t

CK

1, 2, 3, 4

t

RRD

Active bank A to Active bank B command

2

t

CK

1, 2, 3, 4

t

WR

Write recovery time

2

t

CK

1, 2, 3, 4

t

DAL

Auto precharge write recovery + precharge time

5

t

CK

1, 2, 3, 4,

5

t

WTR

Internal write to read command delay

1

t

CK

1, 2, 3, 4

t

XSNR

Exit self-refresh to non-read command

10

t

CK

1, 2, 3, 4

t

XSRD

Exit self-refresh to read command

200

t

CK

1, 2, 3, 4

1. Input slew rate = 1V/ns.

2. The CK/CK input reference level (for timing reference to CK/CK) is the point at which CK and CK cross: the input reference level for

signals other than CK/CK, is V

REF.

3. Inputs are not recognized as valid until V

REF

stabilizes.

4. The Output timing reference level, as measured at the timing reference point indicated in AC Characteristics (Note 3) is V

TT

.

5. t

HZ

and t

LZ

transitions occur in the same access time windows as valid data transitions. These parameters are not referred to a

specific voltage level, but specify when the device is no longer driving (HZ), or begins driving (LZ).

相關PDF資料 |

PDF描述 |

|---|---|

| IBMN625404GT3B | 256Mb Double Data Rate Synchronous DRAM(256M位雙數(shù)據(jù)速率同步動態(tài)RAM) |

| IBMN625804GT3B | 256Mb Double Data Rate Synchronous DRAM(256M位雙數(shù)據(jù)速率同步動態(tài)RAM) |

| ICM7321 | SINGLE 12/10/8-BIT VOLTAGE-OUTPUT DACS |

| ICM7321M | SINGLE 12/10/8-BIT VOLTAGE-OUTPUT DACS |

| ICM7321MG | SINGLE 12/10/8-BIT VOLTAGE-OUTPUT DACS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IBMPPC403GAJC33C1 | 制造商:IBM 功能描述: |

| IBMPPC750CLGEQ4023 | 制造商:IBM 功能描述:MPU 750CL RISC 32BIT 90NM 400MHZ 1.15V/1.8V 278FCBGA - Trays |

| IBMPPC750CLGEQ5023 | 制造商:IBM Microelectronics 功能描述:MPU 750CL RISC 32BIT 90NM 500MHZ 1.15V/1.8V 278FCBGA - Trays |

| IBMPPC750CLGEQA033 | 制造商:IBM 功能描述:MPU 750CL RISC 32BIT 90NM 1GHZ 1.15V/1.8V 278FCBGA - Trays 制造商:IBM 功能描述:IBMIBMPPC750CLGEQA033 CPU PPC 750CL 1GHZ |

| IBN100 | 制造商:Hubbell Wiring Device-Kellems 功能描述:ICON, BLANK,BR,100PK |

發(fā)布緊急采購,3分鐘左右您將得到回復。