- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362819 > IXF440 LAN HUB CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | IXF440 |

| 英文描述: | LAN HUB CONTROLLER |

| 中文描述: | 局域網(wǎng)集線器控制器 |

| 文件頁(yè)數(shù): | 53/100頁(yè) |

| 文件大小: | 1354K |

| 代理商: | IXF440 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)當(dāng)前第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)

IXF440 Multiport 10/100 Mbps Ethernet Controller

Datasheet

53

4.3.2

Header Preprocessing

The IXF440 supports the ability to process the packet header in several ways. The header size is

programmable (RX_PARAM<HDRS>) and may be changed according to the required processing

(for example, MAC header, VLAN header, or Layer3 header).

When header ready mode is enabled (FFO_BUS<HRYD>=0) and a packet header has been fully

loaded into the receive FIFO, the IXF440 will assert the rxrdy signal, even if the header size is

smaller than the programmed receive threshold. In this instance, the first burst of a packet must be

shorter than or equal to the header size.

The packet header may also be read from the receive FIFO for processing without removing it from

the FIFO. If the IXF440 is programmed to work in the header replay mode

(RX_PARAM<HRPL>), the packet header will be transferred twice onto the IX Bus: the first time

for header processing and the second time with the packet transfer.

4.3.3

Packet Segmentation

The IXF440 supports receive packet segmentation on any byte boundaries. When the rxkep signal is

asserted on the last cycle of a burst, the last data transfer of that burst will be reissued on the next burst.

The rxkep signal is ignored when it is asserted in one of the following cases: nonvalid data, last

data of the packet, or last data of the header on header replay mode (RX_PARAM<HRPL>).

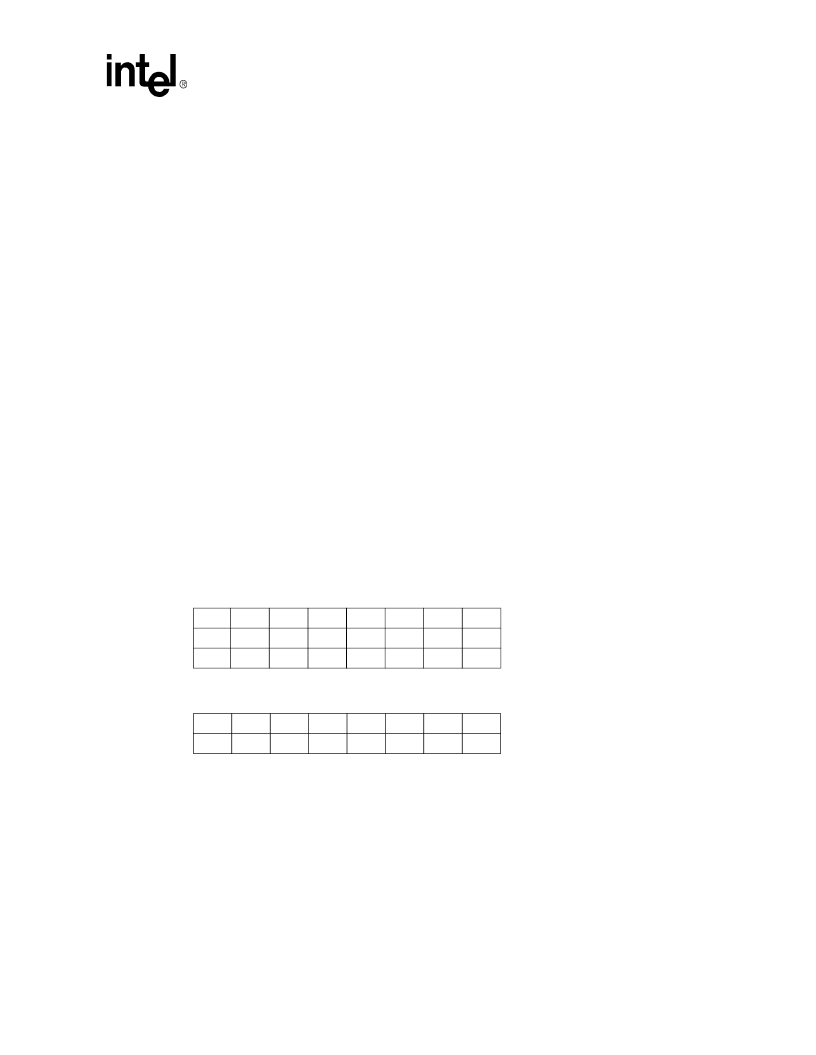

In the example, rxkep is asserted on the last cycle of a three octal word burst from the IXF440,

causing the third octal word to be retained in the receive FIFO. During the next receive burst, this

same octal word will be driven as the first data word of the burst. Any masking of data bytes to the

buffers is performed by the host. In the example, the host places bytes 1

–

19 in the first buffer (a

result of the first burst) and bytes 20

–

28 in the second buffer (a result of the second burst).

Buffer 1:

Buffer 2:

4.3.4

Packet Abortion

During the transfer of a received packet onto the IX Bus, the IXF440 supports the ability to prevent

any further transfer of this packet. At any time during packet reception, the packet may be

dynamically discarded from the receive FIFO by asserting the rxabt signal during packet reading.

Any subsequent packet loaded into the receive FIFO is not affected by rxabt assertion. The next

FIFO access will be the next packet.

B8

B7

B6

B5

B4

B3

B2

B1

B16

B15

B14

B13

B12

B11

B10

B9

X

X

X

X

X

B19

B18

B17

B24

B23

B22

B21

B20

X

X

X

–

replayed

X

X

X

X

B28

B27

B26

B25

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IXF6048 | Telecommunication IC |

| IXFH42N20S | TRANSISTOR | MOSFET | N-CHANNEL | 200V V(BR)DSS | 42A I(D) | TO-247VAR |

| IXFH4N100Q | TRANSISTOR | MOSFET | N-CHANNEL | 1KV V(BR)DSS | 4A I(D) | TO-247AD |

| IXFH50N20S | TRANSISTOR | MOSFET | N-CHANNEL | 200V V(BR)DSS | 50A I(D) | TO-264AA |

| IXFH58N20S | TRANSISTOR | MOSFET | N-CHANNEL | 200V V(BR)DSS | 58A I(D) | TO-247VAR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IXF-45A15AF | 制造商:ILSI 制造商全稱:ILSI America LLC 功能描述:Crystal Filter 3 Lead Metal Package |

| IXF-45A15AT | 制造商:ILSI 制造商全稱:ILSI America LLC 功能描述:Crystal Filter 3 Lead Metal Package |

| IXF-45A15BF | 制造商:ILSI 制造商全稱:ILSI America LLC 功能描述:Crystal Filter 3 Lead Metal Package |

| IXF-45A15BT | 制造商:ILSI 制造商全稱:ILSI America LLC 功能描述:Crystal Filter 3 Lead Metal Package |

| IXF-45A15CF | 制造商:ILSI 制造商全稱:ILSI America LLC 功能描述:Crystal Filter 3 Lead Metal Package |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。