- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374277 > K4N51163QC-ZC (SAMSUNG SEMICONDUCTOR CO. LTD.) 512Mbit gDDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號: | K4N51163QC-ZC |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512Mbit gDDR2 SDRAM |

| 中文描述: | 512MB的GDDR2 SDRAM的 |

| 文件頁數(shù): | 52/64頁 |

| 文件大小: | 1420K |

| 代理商: | K4N51163QC-ZC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當前第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

- 52 -

Rev 1.5 Oct. 2005

512M gDDR2 SDRAM

K4N51163QC-ZC

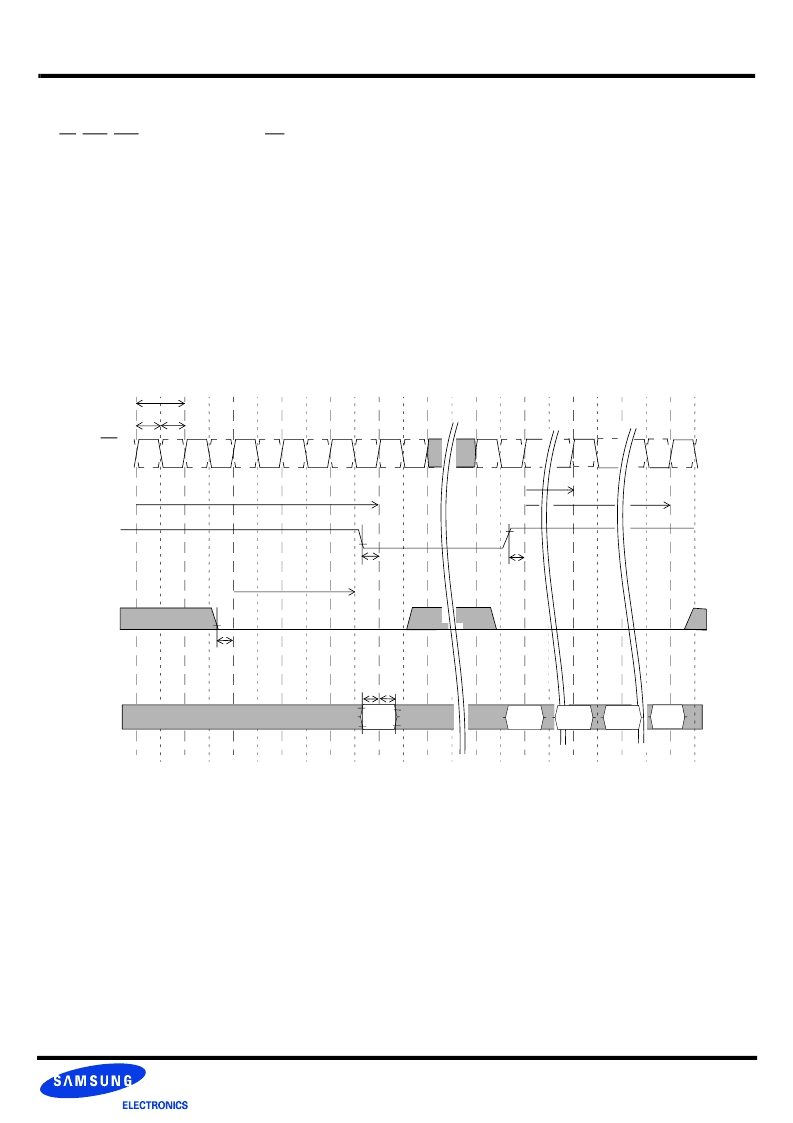

The gDDR2 SDRAM device has a built-in timer to accommodate Self Refresh operation. The Self Refresh Command is defined by hav-

ing CS, RAS, CAS and CKE held low with WE high at the rising edge of the clock. ODT must be turned off before issuing Self Refresh

command, by either driving ODT pin low or using EMRS command. Once the Command is registered, CKE must be held low to keep the

device in Self Refresh mode. When the gDDR2 SDRAM has entered Self Refresh mode all of the external signals except CKE, are

“don’t care”. Since CKE is an SSTL 2 input, V

REF

must be maintained during Self Refresh operation. The DRAM initiates a minimum of

one one Auto Refresh command internally within tCKE period once it enters Self Refresh mode. The clock is internally disabled during

Self Refresh Operation to save power. The minimum time that the gDDR2 SDRAM must remain in Self Refresh mode is tCKE. The user

may change the external clock frequency or halt the external clock one clock after Self-Refresh entry is registered, however, the clock

must be restarted and stable before the device can exit Self Refresh operation. Once Self Refresh Exit command is registered, a delay

equal or longer than the tXSNR or tXSRD must be satisfied before a valid command can be issued to the device. CKE must remain high

for the entire Self Refresh exit period tXSRD for proper operation. Upon exit from Self Refresh, the gDDR2 SDRAM can be put back into

Self Refresh mode after tXSRD expires. NOP or deselect commands must be registered on each positive clock edge during the Self

Refresh exit interval. ODT should also be turned off during tXSRD. Upon exit from Self Refresh, the gDDR2 SDRAM requires a mini-

mum of one extra auto refresh command before it is put back into Self Refresh mode.

- Device must be in the “All banks idle” state prior to entering Self Refresh mode.

- ODT must be turned off tAOFD before entering Self Refresh mode, and can be turned on again when tXSRD timing is satisfied.

- tXSRD is applied for a Read or a Read with autoprecharge command.

- tXSNR is applied for any command except a Read or a Read with autoprecharge command.

CMD

CK

T0

T2

T1

Tm

Tn

CKE

T3

T4

T5

ODT

Self

Refresh

T6

NOP

tAOFD

CK

> = tXSNR

> = tXSRD

tRP*

Valid

tCK

tCH tCL

tIS

tIS

tIS

tIS tIH

NOP

NOP

V

IL

(AC)

V

IL

(AC)

V

IH

(AC)

V

IL

(DC)

V

IH

(AC)

V

IL

(AC)

V

IH

(DC)

Self Refresh Operation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4N51163QC-ZC25 | ; Filter Type:RFI; Current Rating:180A; Voltage Rating:480V; Series:FN258 RoHS Compliant: Yes |

| K4N51163QC-ZC2A | 512Mbit gDDR2 SDRAM |

| K4N51163QC-ZC33 | 512Mbit gDDR2 SDRAM |

| K4N51163QC-ZC36 | 512Mbit gDDR2 SDRAM |

| K4R271669B-N(M)CG6 | 256K x 16/18 bit x 32s banks Direct RDRAMTM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4N51163QC-ZC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mbit gDDR2 SDRAM |

| K4N51163QC-ZC2A | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mbit gDDR2 SDRAM |

| K4N51163QC-ZC33 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mbit gDDR2 SDRAM |

| K4N51163QC-ZC36 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mbit gDDR2 SDRAM |

| K4N51163QG | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:Graphic Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。