- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374280 > K4S51323LF-MC (SAMSUNG SEMICONDUCTOR CO. LTD.) 4M x 32Bit x 4 Banks Mobile SDRAM in 90FBGA PDF資料下載

參數(shù)資料

| 型號: | K4S51323LF-MC |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 4M x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| 中文描述: | 4米× 32Bit的× 4銀行在90FBGA移動SDRAM |

| 文件頁數(shù): | 9/12頁 |

| 文件大小: | 144K |

| 代理商: | K4S51323LF-MC |

K4S51323LF - M(E)C/L/F

September 2004

9

Mobile SDRAM

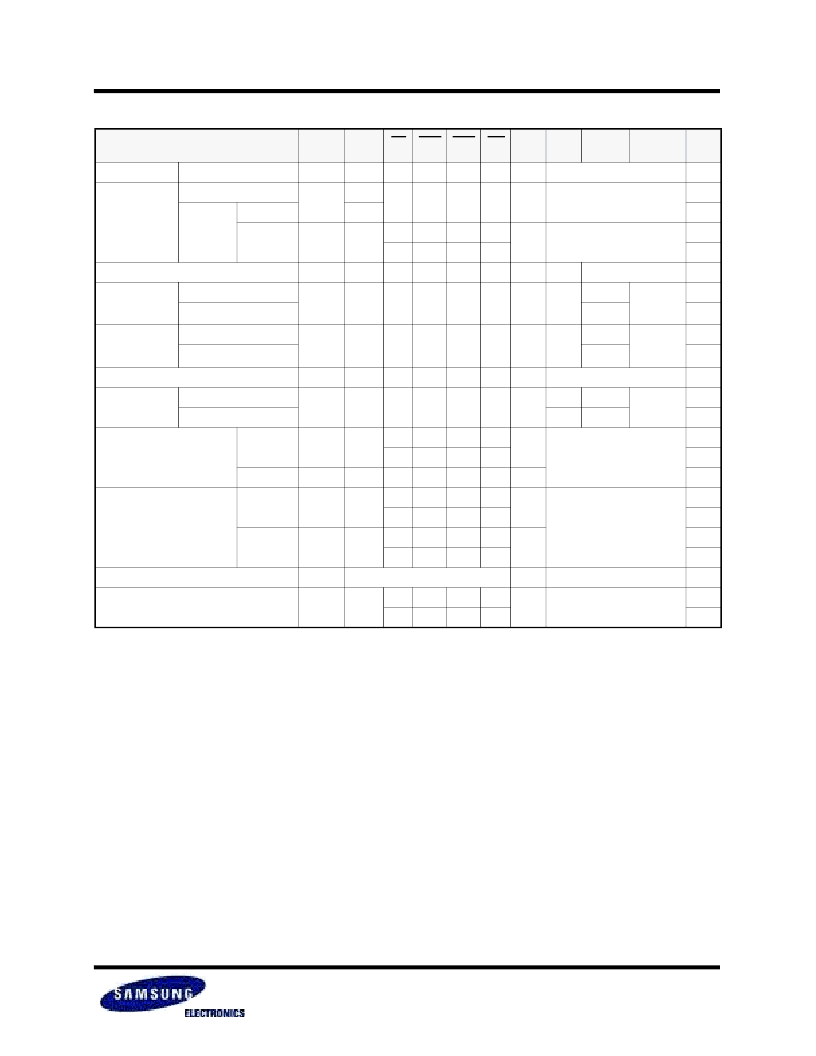

SIMPLIFIED TRUTH TABLE

(V=Valid, X=Don

′

t Care, H=Logic High, L=Logic Low)

NOTES :

1. OP Code : Operand Code

A0 ~ A12 & BA0 ~ BA1 : Program keys. (@MRS)

2. MRS can be issued only at all banks precharge state.

A new command can be issued after 2 CLK cycles of MRS.

3. Auto refresh functions are the same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at all banks precharge state.

Partial self refresh can be issued only after setting partial self refresh mode of EMRS.

4. BA0 ~ BA1 : Bank select addresses.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read/write command can be issued after the end of burst.

New row active of the associated bank can be issued at tRP after the end of burst.

6. Burst stop command is valid at every burst length.

7. DQM sampled at the positive going edge of CLK masks the data-in at that same CLK in write operation (Write DQM latency

is 0), but in read operation, it makes the data-out Hi-Z state after 2 CLK cycles. (Read DQM latency is 2).

COMMAND

CKEn-1 CKEn

CS

RAS

CAS

WE

DQM BA

0,1

A10/AP

A12, A11,

A9 ~ A0

Note

Register

Mode Register Set

H

X

L

L

L

L

X

OP CODE

1, 2

Refresh

Auto Refresh

H

H

L

L

L

H

X

X

3

Self

Refresh

Entry

L

3

Exit

L

H

L

H

H

H

X

X

3

H

X

X

X

3

Bank Active & Row Addr.

H

X

L

L

H

H

X

V

Row Address

Read &

Column Address

Auto Precharge Disable

H

X

L

H

L

H

X

V

L

Column

Address

(A0~A8)

Column

Address

(A0~A8)

4

Auto Precharge Enable

H

4, 5

Write &

Column Address

Auto Precharge Disable

H

X

L

H

L

L

X

V

L

4

Auto Precharge Enable

H

4, 5

Burst Stop

H

X

L

H

H

L

X

X

6

Precharge

Bank Selection

H

X

L

L

H

L

X

V

L

X

All Banks

X

H

Clock Suspend or

Active Power Down

Entry

H

L

H

X

X

X

X

X

L

V

V

V

Exit

L

H

X

X

X

X

X

Precharge Power Down

Mode

Entry

H

L

H

X

X

X

X

X

L

H

H

H

Exit

L

H

H

X

X

X

X

L

V

V

V

DQM

H

X

V

X

7

No Operation Command

H

X

H

X

X

X

X

X

L

H

H

H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4S51323LF-F1L | connector |

| K4S51323LF-L | 4M x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S560432D | 16M x 4bit x 4 Banks Synchronous DRAM LVTTL |

| K4S560432D-TC1H | 16M x 4bit x 4 Banks Synchronous DRAM LVTTL |

| K4S560432D-TC1L | 16M x 4bit x 4 Banks Synchronous DRAM LVTTL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4S51323P | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 32Bit x 4 Banks Mobile-SDRAM |

| K4S51323PF-MEF1L | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 32Bit x 4 Banks Mobile-SDRAM |

| K4S51323PF-MEF75 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 32Bit x 4 Banks Mobile-SDRAM |

| K4S51323PF-MEF90 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 32Bit x 4 Banks Mobile-SDRAM |

| K4S51323PF-MF1L | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 32Bit x 4 Banks Mobile-SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。