- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374293 > K7D323674A-HGC37 (SAMSUNG SEMICONDUCTOR CO. LTD.) 32Mb A-die DDR SRAM Specification PDF資料下載

參數(shù)資料

| 型號: | K7D323674A-HGC37 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 32Mb A-die DDR SRAM Specification |

| 中文描述: | 32兆甲芯片的DDR SRAM的規(guī)范 |

| 文件頁數(shù): | 4/19頁 |

| 文件大小: | 494K |

| 代理商: | K7D323674A-HGC37 |

Rev 1.4

Oct. 2005

1Mx36 & 2Mx18 SRAM

- 4 -

K7D321874A

K7D323674A

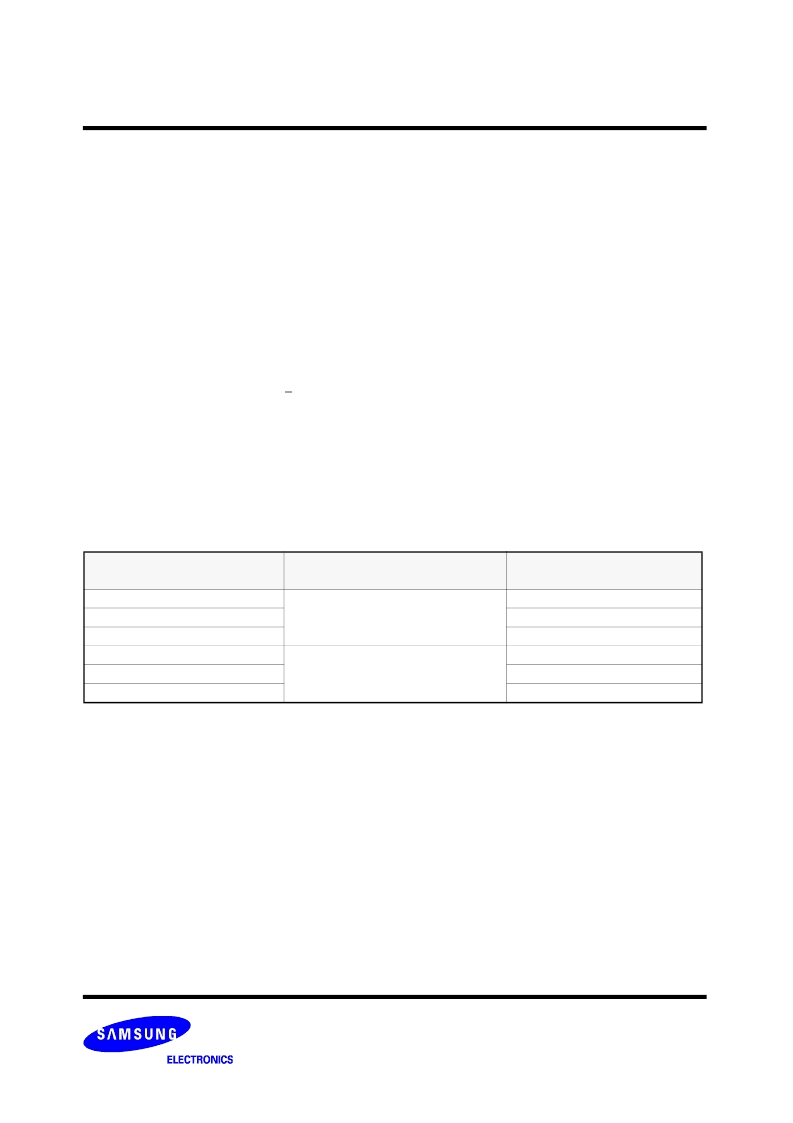

ORDERING INFORMATION

Part Number

Organization

Maximum

Frequency

K7D323674A-H(G)C40

1Mx36

400MHz

K7D323674A-H(G)C37

375MHz

K7D323674A-H(G)C33

333MHz

K7D321874A-H(G)C40

2Mx18

400MHz

K7D321874A-H(G)C37

375MHz

K7D321874A-H(G)C33

333MHz

GENERAL DESCRIPTION

The K7D323674A and K7D321874A are 37,748,736 bit Synchronous Pipeline Burst Mode SRAM devices. They are organized as

1,048,576 words by 36 bits for K7D323674A and 2,097,152 words by 18 bits for K7D321874A, fabricated using Samsung's

advanced CMOS technology.

Single differential HSTL level clock, K and K are used to initiate the read/write operation and all internal operations are self-timed. At

the rising edge of K clock, all addresses and burst control inputs are registered internally. Data inputs are registered one cycle after

write addresses are asserted(Late Write), at the rising edge of K clock for single data rate (SDR) write operations and at rising and

falling edge of K clock for a double data rate (DDR) write operations.

Data outputs are updated from output registers off the rising edges of K clock for SDR read operations and off the rising and falling

edges of K clock for DDR read operations. Free running echo clocks are supported which are representative of data output access

time for all SDR and DDR operations.

The chip is operated with 1.8~2.5V power supply and is compatible with HSTL input and output. The package is 9x17(153) Ball Grid

Array balls on a 1.27mm pitch.

FEATURES

1Mx36 or 2Mx18 Organizations.

1.8~2.5V V

DD

/1.5V ~1.8V

DDQ

.

HSTL Input and Outputs.

Single Differential HSTL Clock.

Synchronous Pipeline Mode of Operation with Self-Timed

Late Write.

Free Running Active High and Active Low Echo Clock Output

Pin.

Registered Addresses, Burst Control and Data Inputs.

Registered Outputs.

Double and Single Data Rate Burst Read and Write.

Burst Count Controllable With Max Burst Length of 4

Interleved and Linear Burst mode support

Bypass Operation Support

Programmable Impedance Output Drivers.

JTAG Boundary Scan (subset of IEEE std. 1149.1)

153(9x17) Flip Chip Ball Grid Array Package(14mmx22mm)

No Output enable support.

* G : Lead free package

相關PDF資料 |

PDF描述 |

|---|---|

| K7D323674A-HGC40 | 32Mb A-die DDR SRAM Specification |

| K7D801871B-HC25 | 256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC30 | 256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC33 | 256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC35 | 256Kx36 & 512Kx18 SRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| K7D323674A-HGC40 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Mb A-die DDR SRAM Specification |

| K7D323674C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 SRAM |

| K7D801871B-HC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC30 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC33 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。