- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374293 > K7D323674A-HGC40 (SAMSUNG SEMICONDUCTOR CO. LTD.) 32Mb A-die DDR SRAM Specification PDF資料下載

參數(shù)資料

| 型號(hào): | K7D323674A-HGC40 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 32Mb A-die DDR SRAM Specification |

| 中文描述: | 32兆甲芯片的DDR SRAM的規(guī)范 |

| 文件頁(yè)數(shù): | 14/19頁(yè) |

| 文件大?。?/td> | 494K |

| 代理商: | K7D323674A-HGC40 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

Rev 1.4

Oct. 2005

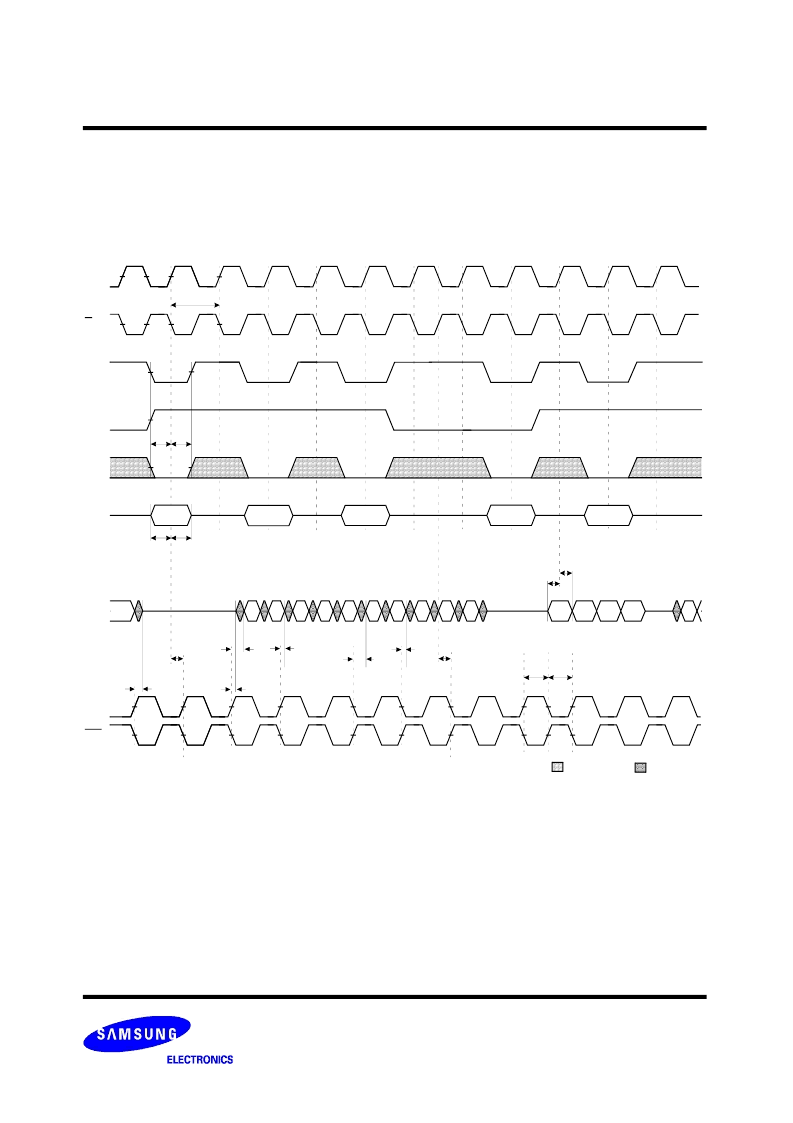

1Mx36 & 2Mx18 SRAM

- 14

K7D321874A

K7D323674A

NOP

CONTINUE

K

K

B1

SA

t

AVKH

t

KHAX

CQ

NOP

1

2

3

4

5

6

7

8

10

12

11

B2

B3

CQ

DQ

READ

(burst of 4)

(burst of 4)

READ

(burst of 2)

READ

NOP

WRITE

CONTINUE

WRITE

(burst of 4)

READ

9

CONTINUE

READ

READ

(burst of 4)

CONTINUE

READ

A

0

A

1

A

2

A

3

Q

X2

Q

01

Q

02

Q

03

Q

04

Q

51

Q

52

Q

53

Q

54

Q

11

Q

12

D

21

D

23

D

24

D

22

Q

31

t

BVKH

t

KHBX

t

CHQZ

t

KXCH

t

CHLZ

t

CHQV

t

CHQX

t

DVKH

t

KHDX

t

KHKH

UNDEFINED

DON’T CARE

A

5

NOTE

1. Q

01

refers to output from address A. Q

02

refers to output from the next internal burst address following A, etc.

2. Outputs are disabled(High-Z) one clock cycle after NOP detected or after no pending data requests are present.

3. Doing more than one Read Continue or Write Continue will cause the address to wrap around.

TIMING WAVEFORMS FOR DOUBLE DATA RATE CYCLES

(Burst Length=4, 2)

t

CLQV

t

CLQX

t

KXCL

t

CHCL

t

CLCH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7D801871B-HC25 | 256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC30 | 256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC33 | 256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC35 | 256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC37 | 256Kx36 & 512Kx18 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7D323674C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 SRAM |

| K7D801871B-HC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC30 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC33 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 SRAM |

| K7D801871B-HC35 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。