- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374293 > K7D323674A (SAMSUNG SEMICONDUCTOR CO. LTD.) 32Mb A-die DDR SRAM Specification PDF資料下載

參數(shù)資料

| 型號: | K7D323674A |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 32Mb A-die DDR SRAM Specification |

| 中文描述: | 32兆甲芯片的DDR SRAM的規(guī)范 |

| 文件頁數(shù): | 17/19頁 |

| 文件大?。?/td> | 494K |

| 代理商: | K7D323674A |

Rev 1.4

Oct. 2005

1Mx36 & 2Mx18 SRAM

- 17

K7D321874A

K7D323674A

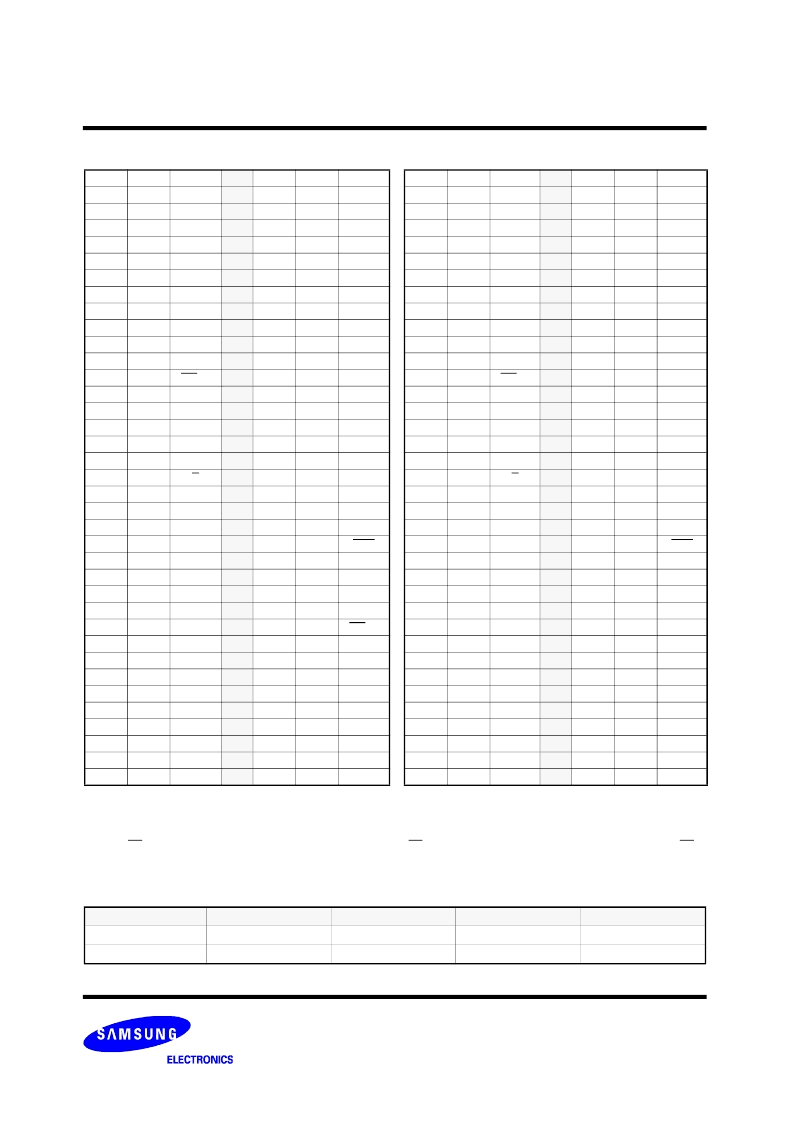

BOUNDARY SCAN EXIT ORDER(x36)

* Reserved for Mode Pin

1

5P

5R

5T

6R

7T

7R

7P

8T

9T

8P

7M

9P

8M

9M

7K

8K

9K

6L

5H

5G

9H

8H

7H

9F

8F

9D

7F

8D

9B

8B

7D

7C

7B

7A

6D

6C

6A

V

DD

(2)

SA

1

SA

0

SA

SA

V

DD

(2)

SA

DQ1

DQ2

DQ10

DQ0

DQ12

CQ(3)

DQ3

DQ9

DQ11

DQ13

MODE

K

K

DQ4

DQ6

DQ8

DQ14

CQ(3)

DQ5

DQ17

DQ7

DQ15

DQ16

SA

SA

SA

SA

V

SS

(2)

SA

SA

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

5C

4A

4C

4D

3A

3B

3C

3D

2B

1B

2D

3F

1D

2F

1F

3H

2H

1H

5A

5B

5K

5L

4L

1K

2K

3K

1M

2M

1P

3M

2P

1T

2T

3R

3T

4R

SA

SA

SA

V

SS

(2

SA

SA

SA

SA

DQ19

DQ20

DQ28

DQ18

DQ30

CQ(3)

DQ21

DQ27

DQ29

DQ31

ZQ(1)

B

1

B

2

B

3

LBO

DQ22

DQ24

DQ26

DQ32

CQ(3)

DQ23

DQ35

DQ25

DQ33

DQ34

V

DD

(2)

SA

SA

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

74

7U

NC

BOUNDARY SCAN EXIT ORDER(x18)

* Reserved for Mode Pin

1

2

3

4

5

6

7

8

5P

5R

5T

6R

7T

7R

7P

8T

V

DD

(2)

SA

1

SA

0

SA

SA

V

DD

(2)

SA

DQ1

28

29

30

31

32

33

34

35

36

5C

4A

4C

4D

3A

3B

3C

3D

2B

SA

SA

SA

V

SS

(2)

SA

SA

SA

SA

DQ10

9

9P

8M

DQ2

CQ(3)

10

37

38

1D

2F

DQ11

CQ(3)

11

7K

DQ0

39

3H

DQ9

12

13

14

15

9K

6L

5H

5G

DQ3

MODE

K

K

40

41

42

43

44

45

1H

5A

5B

5K

5L

4L

DQ12

ZQ(1)

B1

B2

B3

LBO

16

8H

DQ6

17

9F

DQ4

46

2K

DQ15

18

19

20

7F

8D

9B

DQ8

DQ7

DQ5

47

1M

DQ13

48

49

50

51

52

53

54

55

3M

2P

1T

3P

3R

3T

4R

7U

DQ17

DQ16

DQ14

SA

V

DD

(2)

SA

SA

NC

21

22

23

24

25

26

27

7D

7C

7B

7A

6D

6C

6A

SA

SA

SA

SA

V

SS

(2)

SA

SA

NOTE

:

1. If pin is connected as they should, TDO will be low. If pin is open, TDO will be high

2. This pin is place holder for higher density. TDO will be low for V

SS

and high for V

DD

3. CQ and CQ are outputs during boundary scan. CQ reflects the input to K and CQ outputs the inverted value of K. It is prohibited to force CQ and CQ.

And TDO is ’X’.(Don’t Care)

SCAN REGISTER DEFINITION

Part

Instruction Register

Bypass Register

ID Register

Boundary Scan

1M x 36

3 bits

1 bits

32 bits

74 bits

2M x 18

3 bits

1 bits

32 bits

55 bits

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7D323674A-HC33 | 32Mb A-die DDR SRAM Specification |

| K7D323674A-HC37 | 32Mb A-die DDR SRAM Specification |

| K7D323674A-HC40 | 32Mb A-die DDR SRAM Specification |

| K7D323674A-HGC33 | 32Mb A-die DDR SRAM Specification |

| K7D323674A-HGC37 | 32Mb A-die DDR SRAM Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7D323674A-HC33 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Mb A-die DDR SRAM Specification |

| K7D323674A-HC37 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Mb A-die DDR SRAM Specification |

| K7D323674A-HC40 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Mb A-die DDR SRAM Specification |

| K7D323674A-HGC33 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Mb A-die DDR SRAM Specification |

| K7D323674A-HGC37 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Mb A-die DDR SRAM Specification |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。