- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374293 > K7J641882M-FC25 (SAMSUNG SEMICONDUCTOR CO. LTD.) 72Mb M-die DDRII SRAM Specification PDF資料下載

參數(shù)資料

| 型號(hào): | K7J641882M-FC25 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 72Mb M-die DDRII SRAM Specification |

| 中文描述: | 72Mb的M -模條DDRII規(guī)格的SRAM |

| 文件頁(yè)數(shù): | 4/17頁(yè) |

| 文件大?。?/td> | 326K |

| 代理商: | K7J641882M-FC25 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

2Mx36 & 4Mx18 DDR II SIO b2 SRAM

K7J643682M

K7J641882M

- 4 -

Rev 1.0

Aug. 2005

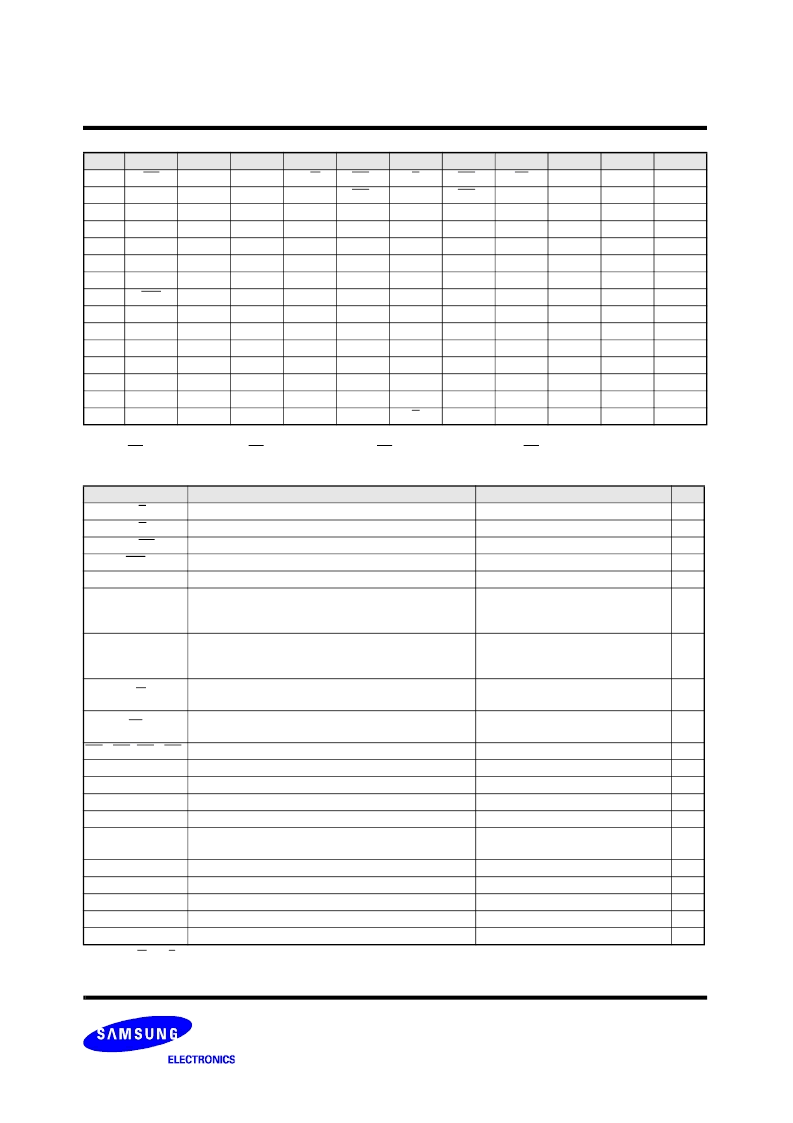

PIN CONFIGURATIONS

(TOP VIEW)

K7J643682M(2Mx36)

Notes :

1. * Checked No Connect(NC) pins are reserved for higher density address, i.e. 10A for 144Mb and 2A for 288Mb.

2. BW

0

controls write to D0:D8, BW

1

controls write to D9:D17, BW

2

controls write to D18:D26 and BW

3

controls write to D27:D35.

1

2

3

4

5

6

K

K

SA

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

SA

C

C

7

8

9

10

11

CQ

Q8

D8

D7

Q6

Q5

D5

ZQ

D4

Q3

Q2

D2

D1

Q0

TDI

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

CQ

Q27

D27

D28

Q29

Q30

D30

Doff

D31

Q32

Q33

D33

D34

Q35

TDO

V

SS/

SA*

Q18

Q28

D20

D29

Q21

D22

V

REF

Q31

D32

Q24

Q34

D26

D35

TCK

SA

D18

D19

Q19

Q20

D21

Q22

V

DDQ

D23

Q23

D24

D25

Q25

Q26

SA

R/W

SA

V

SS

V

SS

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

SS

V

SS

SA

SA

BW

2

BW

3

SA

V

SS

V

SS

V

DD

V

DD

V

DD

V

DD

V

DD

V

SS

V

SS

SA

SA

SA

BW

1

BW

0

SA

V

SS

V

SS

V

DD

V

DD

V

DD

V

DD

V

DD

V

SS

V

SS

SA

SA

SA

LD

SA

V

SS

V

SS

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

SS

V

SS

SA

SA

SA

D17

D16

Q16

Q15

D14

Q13

V

DDQ

D12

Q12

D11

D10

Q10

Q9

SA

V

SS/

SA*

Q17

Q7

D15

D6

Q14

D13

V

REF

Q4

D3

Q11

Q1

D9

D0

TMS

PIN NAME

Notes:

1. C, C, K or K cannot be set to V

REF

voltage.

2. When ZQ pin is directly connected to V

DD

output impedance is set to minimum value

and it

cannot be connected to ground or left unconnected

.

3. Not connected to chip pad internally.

SYMBOL

K, K

C, C

CQ, CQ

Doff

SA

PIN NUMBERS

6B, 6A

6P, 6R

11A, 1A

1H

DESCRIPTION

Input Clock

Input Clock for Output Data

Output Echo Clock

DLL Disable when low

Address Inputs

NOTE

1

3A,9A,4B,8B,5C-7C,5N-7N,4P,5P,7P,8P,3R-5R,7R-9R

10P,11N,11M,10K,11J,11G,10E,11D,11C,10N,9M,9L

9J,10G,9F,10D,9C,9B,3B,3C,2D,3F,2G,3J,3L,3M,2N

1C,1D,2E,1G,1J,2K,1M,1N,2P

D0-35

Data Inputs

Q0-35

11P,10M,11L,11K,10J,11F,11E,10C,11B,9P,9N,10L

9K,9G,10F,9E,9D,10B,2B,3D,3E,2F,3G,3K,2L,3N

3P,1B,2C,1E,1F,2J,1K,1L,2M,1P

Data Outputs

R/W

4A

Read, Write Control Pin, Read active

when high

LD

8A

Synchronous Load Pin, bus Cycle

sequence is to be defined when low

BW

0

, BW

1,

BW

2

, BW

3

V

REF

ZQ

V

DD

V

DDQ

7B,7A,5A,5B

2H,10H

11H

Block Write Control Pin,active when low

Input Reference Voltage

Output Driver Impedance Control Input

Power Supply ( 1.8 V )

Output Power Supply ( 1.5V or 1.8V )

2

5F,7F,5G,7G,5H,7H,5J,7J,5K,7K

4E,8E,4F,8F,4G,8G,3H,4H,8H,9H,4J,8J,4K,8K,4L,8L

2A,10A,4C,8C,4D-8D,5E-7E,6F,6G,6H,6J,6K,5L-7L,4M,

8M,4N,8N

V

SS

Ground

TMS

TDI

TCK

TDO

NC

10R

11R

2R

1R

-

JTAG Test Mode Select

JTAG Test Data Input

JTAG Test Clock

JTAG Test Data Output

No Connect

3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7J641882M-FC30 | 72Mb M-die DDRII SRAM Specification |

| K7J641882M-FECI16 | 72Mb M-die DDRII SRAM Specification |

| K7J641882M-FECI20 | 72Mb M-die DDRII SRAM Specification |

| K7J641882M-FECI25 | 72Mb M-die DDRII SRAM Specification |

| K7J641882M-FECI30 | 72Mb M-die DDRII SRAM Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7J641882M-FC30 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:72Mb M-die DDRII SRAM Specification |

| K7J641882M-FECI16 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:72Mb M-die DDRII SRAM Specification |

| K7J641882M-FECI20 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:72Mb M-die DDRII SRAM Specification |

| K7J641882M-FECI25 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:72Mb M-die DDRII SRAM Specification |

| K7J641882M-FECI30 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:72Mb M-die DDRII SRAM Specification |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。