- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374294 > K7R321884M (SAMSUNG SEMICONDUCTOR CO. LTD.) 1Mx36 & 2Mx18 QDRTM II b4 SRAM PDF資料下載

參數(shù)資料

| 型號: | K7R321884M |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 1Mx36 & 2Mx18 QDRTM II b4 SRAM |

| 中文描述: | 1Mx36 |

| 文件頁數(shù): | 13/18頁 |

| 文件大?。?/td> | 195K |

| 代理商: | K7R321884M |

- 13 -

Rev 2.0

Dec. 2003

1Mx36 & 2Mx18 QDR

TM

II b4 SRAM

K7R323684M

K7R321884M

t

KLKH

t

KHKH

t

KHKH

t

KHKL

t

AVKH

t

KHAX

A1

A2

t

IVKH

t

KHIX

Q1-1

Q1-2

Q1-3

Q1-4

Q2-3

t

CHQX

1

t

KHCH

t

CHQV

t

CHQX

t

CQHQV

t

CQHQX

t

CHCQX

t

CHCQV

t

CHQV

t

CHCQX

t

CHCQV

t

KLKH

t

KHKH

t

KHKL

t

KHKH

Note

:

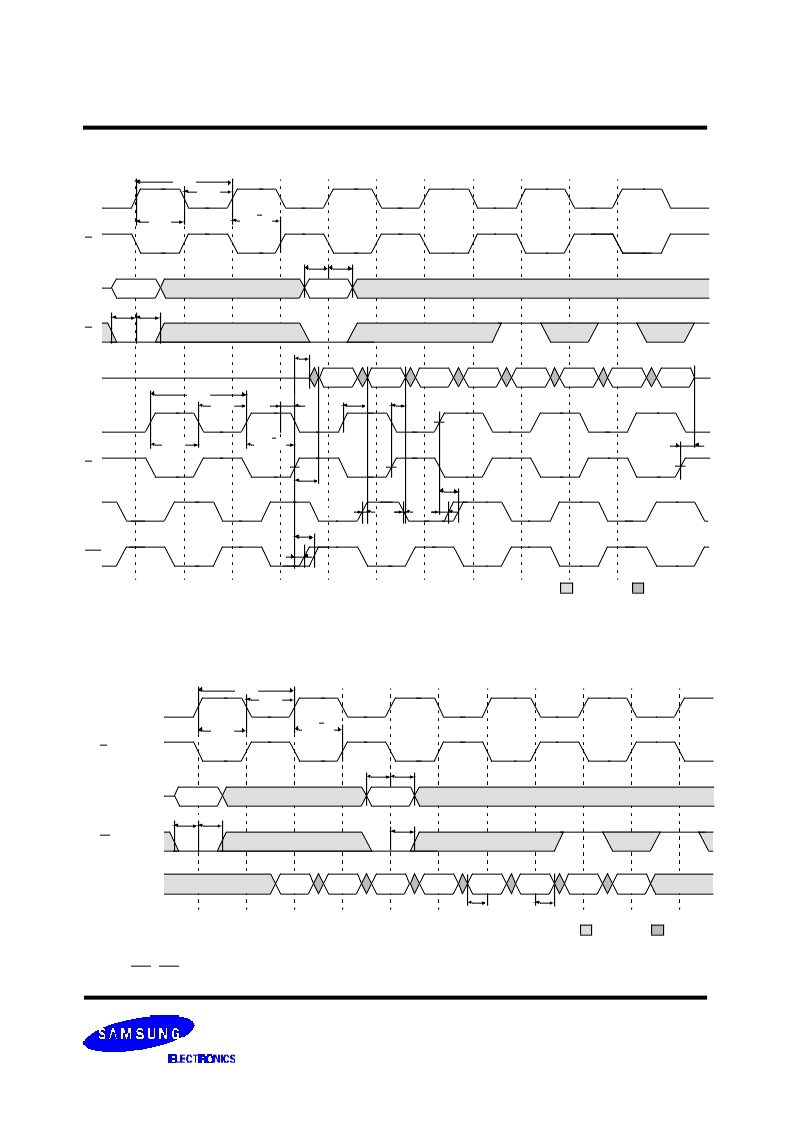

1. Q1-1 refers to output from address A1+0, Q1-2 refers to output from address A1+1 i.e. the next internal burst address following A1+0.

2. Outputs are disabled one cycle after a NOP.

K

SA

R

K

Q

(Data Out)

C

C

TIMING WAVE FORMS OF READ AND NOP

Don

′

t Care Undefined

CQ

CQ

Q2-1

Q2-2

D1-1

D1-2

D1-3

D1-4

K

SA

W

K

D(Data In)

TIMING WAVE FORMS OF WRITE AND NOP

WRITE

D2-1

D2-2

t

DVKH

t

KHDX

Don

′

t Care Undefined

Note

:

1. D1-1 refers to input to address A1+0, D1-2 refers to input to address A1+1, i.e the next internal burst address following A1+0.

2. BWx ( NWx ) assumed active.

t

KLKH

t

KHKH

t

KHKH

t

KHKL

t

AVKH

t

KHAX

A1

A2

t

IVKH

t

KHIX

D2-3

D2-4

t

KHIX

Q2-4

t

CHQZ

READ

NOP

NOP

READ

NOP

NOP

WRITE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7R321884M-FC20 | 1Mx36 & 2Mx18 QDRTM II b4 SRAM |

| K7R321884M-FC25 | 1Mx36 & 2Mx18 QDRTM II b4 SRAM |

| K7R640982M | 2Mx36 & 4Mx18 & 8Mx9 QDRTM II b2 SRAM |

| K7R641882M | Electrical, Duct/Raceway (Trunking); RoHS Compliant: Yes |

| K7R643682M | 2Mx36 & 4Mx18 & 8Mx9 QDRTM II b2 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7R321884M-FC16 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 QDRTM II b4 SRAM |

| K7R321884M-FC20 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 QDRTM II b4 SRAM |

| K7R321884M-FC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 QDRTM II b4 SRAM |

| K7R323682 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 & 4Mx9 QDRTM II b2 SRAM |

| K7R323682C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 & 4Mx9 QDR II b2 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。