- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374296 > K9F1208UOM (SAMSUNG SEMICONDUCTOR CO. LTD.) 64M x 8 Bit NAND Flash Memory(64M x 8位與非閃速存儲(chǔ)器) PDF資料下載

參數(shù)資料

| 型號(hào): | K9F1208UOM |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 64M x 8 Bit NAND Flash Memory(64M x 8位與非閃速存儲(chǔ)器) |

| 中文描述: | 6400 × 8位NAND閃存(64米× 8位與非閃速存儲(chǔ)器) |

| 文件頁數(shù): | 29/41頁 |

| 文件大小: | 1006K |

| 代理商: | K9F1208UOM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

K9F1208U0M-YCB0, K9F1208U0M-YIB0

FLASH MEMORY

29

Device Operation

PAGE READ

Upon initial device power up, the device defaults to Read1 mode. This operation is also initiated by writing 00h to the command reg-

ister along with four address cycles. Once the command is latched, it does not need to be written for the following page read opera-

tion. Three types of operations are available : random read, serial page read and sequential row read.

The random read mode is enabled when the page address is changed. The 528 bytes of data within the selected page are trans-

ferred to the data registers in less than 12

μ

s(t

R

). The system controller can detect the completion of this data transfer(tR) by analyz-

ing the output of R/B pin. Once the data in a page is loaded into the registers, they may be read out in 50ns cycle time by sequentially

pulsing RE. High to low transitions of the RE clock output the data stating from the selected column address up to the last column

address.

After the data of last column address is clocked out, the next page is automatically selected for sequential row read.

Waiting 12

μ

s again allows reading the selected page. The sequential row read operation is terminated by bringing CE high. The

way the Read1 and Read2 commands work is like a pointer set to either the main area or the spare area. The spare area of bytes

512 to 527 may be selectively accessed by writing the Read2 command. Addresses A

0

to A

3

set the starting address of the spare

area while addresses A

4

to A

7

are ignored. Unless the operation is aborted, the page address is automatically incremented for

sequential row read as in Read1 operation and spare sixteen bytes of each page may be sequentially read. The Read1 com-

mand(00h/01h) is needed to move the pointer back to the main area. Figures 3 to 6 show typical sequence and timings for each read

operation.

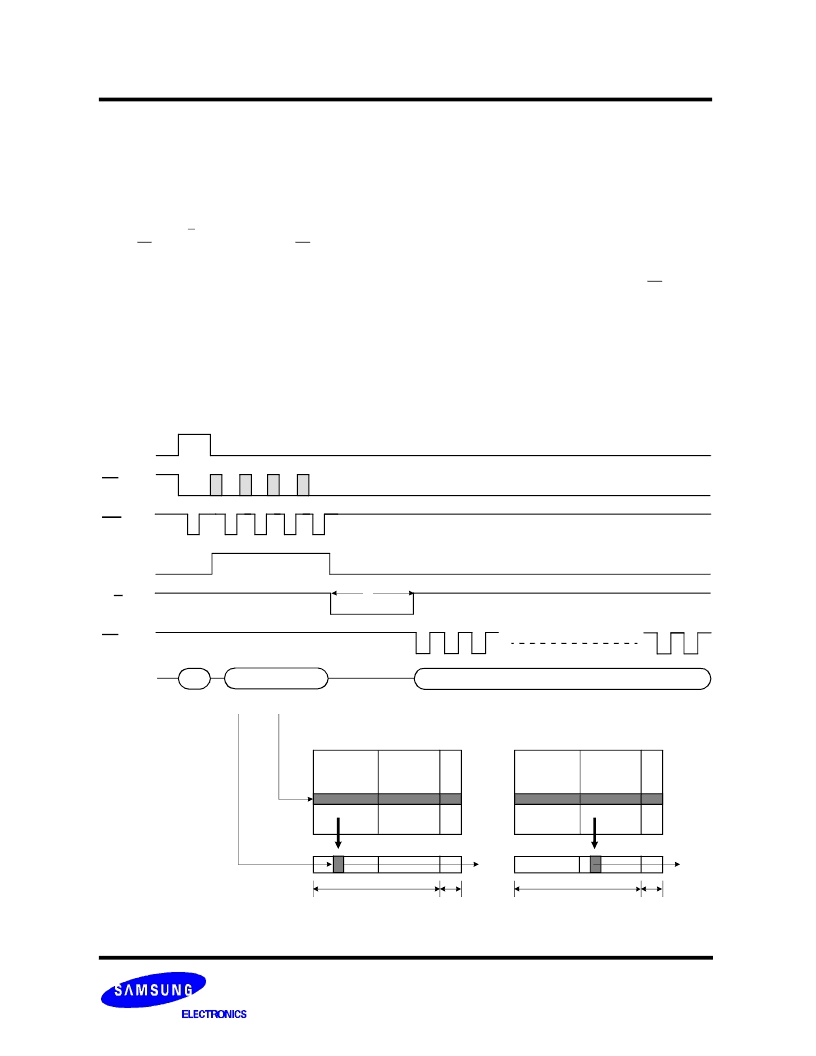

Figure 3. Read1 Operation

Start Add.(4Cycle)

00h

A

0

~ A

7

& A

9

~ A

25

Data Output(Sequential)

(00h Command)

Data Field

Spare Field

CE

CLE

ALE

R/B

WE

I/O

0

~

7

RE

t

R

* After data access on 2nd half array by 01h command, the start pointer is automatically moved to 1st half

array (00h) at next cycle.

(01h Command)*

Data Field

Spare Field

1st half array

2st half array

1st half array

2st half array

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K9F1608W0A- | 2M x 8 Bit NAND Flash Memory |

| K9F1608W0A-TCB0 | TV 128C 128#22D SKT RECP |

| K9F1608W0A-TIB0 | TV 37C 37#16 PIN RECP |

| K9F1G08Q0A | FLASH MEMORY |

| K9F1G08U0A | FLASH MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K9F1208UOMYCB0 | 制造商:SAMSUNG 功能描述:K9F1208UOM-YCB0 |

| K9F1208UOM-YCB0 | 制造商:SAMSUNG 功能描述:K9F1208UOM-YCB0 |

| K9F1208X0A | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64M x 8 Bit , 32M x 16 Bit NAND Flash Memory |

| K9F1208X0C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64M x 8 Bits NAND Flash Memory |

| K9F1216D0A | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64M x 8 Bit , 32M x 16 Bit NAND Flash Memory |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。