- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374354 > KM416S16230A (SAMSUNG SEMICONDUCTOR CO. LTD.) 4M x 16Bit x 4 Banks Synchronous DRAM(4M x 16位 x4組同步動態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號: | KM416S16230A |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 4M x 16Bit x 4 Banks Synchronous DRAM(4M x 16位 x4組同步動態(tài)RAM) |

| 中文描述: | 4米× 16 × 4銀行同步DRAM(4米× 16位x4組同步動態(tài)RAM)的 |

| 文件頁數(shù): | 6/8頁 |

| 文件大小: | 62K |

| 代理商: | KM416S16230A |

KM416S16230A

CMOS SDRAM

REV. 0 May '98

Preliminary

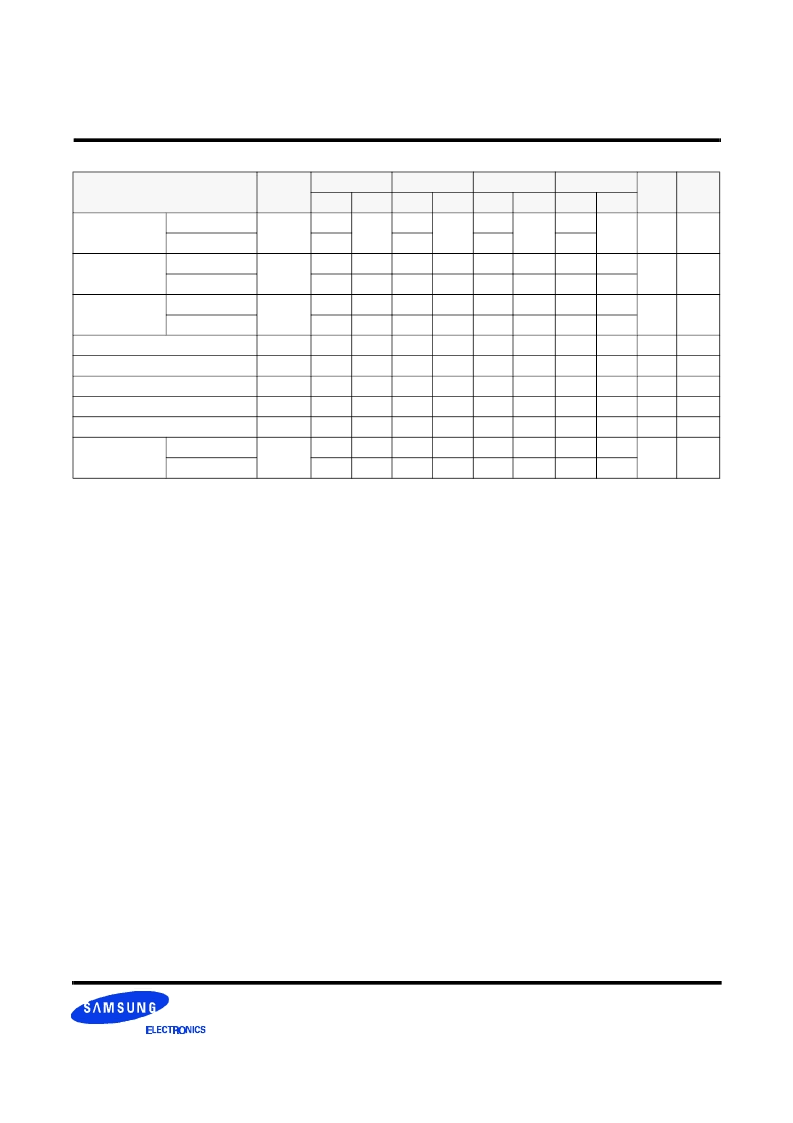

AC CHARACTERISTICS

(AC operating conditions unless otherwise noted)

Parameter

Symbol

-8

-H

-L

-10

Unit

Note

Min

Max

Min

Max

Min

Max

Min

Max

CLK cycle time

CAS latency=3

t

CC

8

1000

10

1000

10

1000

10

1000

ns

1

CAS latency=2

12

10

12

13

CLK to valid

output delay

CAS latency=3

t

SAC

6

6

6

7

ns

1,2

CAS latency=2

6

6

7

7

Output data

hold time

CAS latency=3

t

OH

3

3

3

3

ns

2

CAS latency=2

3

3

3

3

CLK high pulse width

t

CH

3

3

3

3.5

ns

3

CLK low pulse width

t

CL

3

3

3

3.5

ns

3

Input setup time

t

SS

2

2

2

2.5

ns

3

Input hold time

t

SH

1

1

1

1.5

ns

3

CLK to output in Low-Z

t

SLZ

1

1

1

1

ns

2

CLK to output

in Hi-Z

CAS latency=3

t

SHZ

6

6

6

7

ns

CAS latency=2

6

6

7

7

1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

Notes :

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM416S4030C | 1M x 16Bit x 4 Banks Synchronous DRAM |

| KM416S4030CT-F10 | 1M x 16Bit x 4 Banks Synchronous DRAM |

| KM416S4030CT-F7 | 1M x 16Bit x 4 Banks Synchronous DRAM |

| KM416S4030CT-F8 | 1M x 16Bit x 4 Banks Synchronous DRAM |

| KM416S4030CT-FH | 1M x 16Bit x 4 Banks Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM416S1DTG8T | 制造商:Panasonic Industrial Company 功能描述:IC |

| KM416S4020AT-G10 | 制造商:Samsung Semiconductor 功能描述: |

| KM416S4020BT-GL | 制造商:Samsung Semiconductor 功能描述: |

| KM416S4030C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1M x 16Bit x 4 Banks Synchronous DRAM |

| KM416S4030CT-F10 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1M x 16Bit x 4 Banks Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。