- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄34741 > 7303J11CGI32 (ITT CANNON) ROCKER SWITCH, 3PDT, LATCHED, 5A, 28VDC, THROUGH HOLE-STRAIGHT PDF資料下載

參數(shù)資料

| 型號: | 7303J11CGI32 |

| 廠商: | ITT CANNON |

| 元件分類: | 開關(guān) |

| 英文描述: | ROCKER SWITCH, 3PDT, LATCHED, 5A, 28VDC, THROUGH HOLE-STRAIGHT |

| 封裝: | ROHS COMPLIANT |

| 文件頁數(shù): | 4/22頁 |

| 文件大?。?/td> | 1631K |

| 代理商: | 7303J11CGI32 |

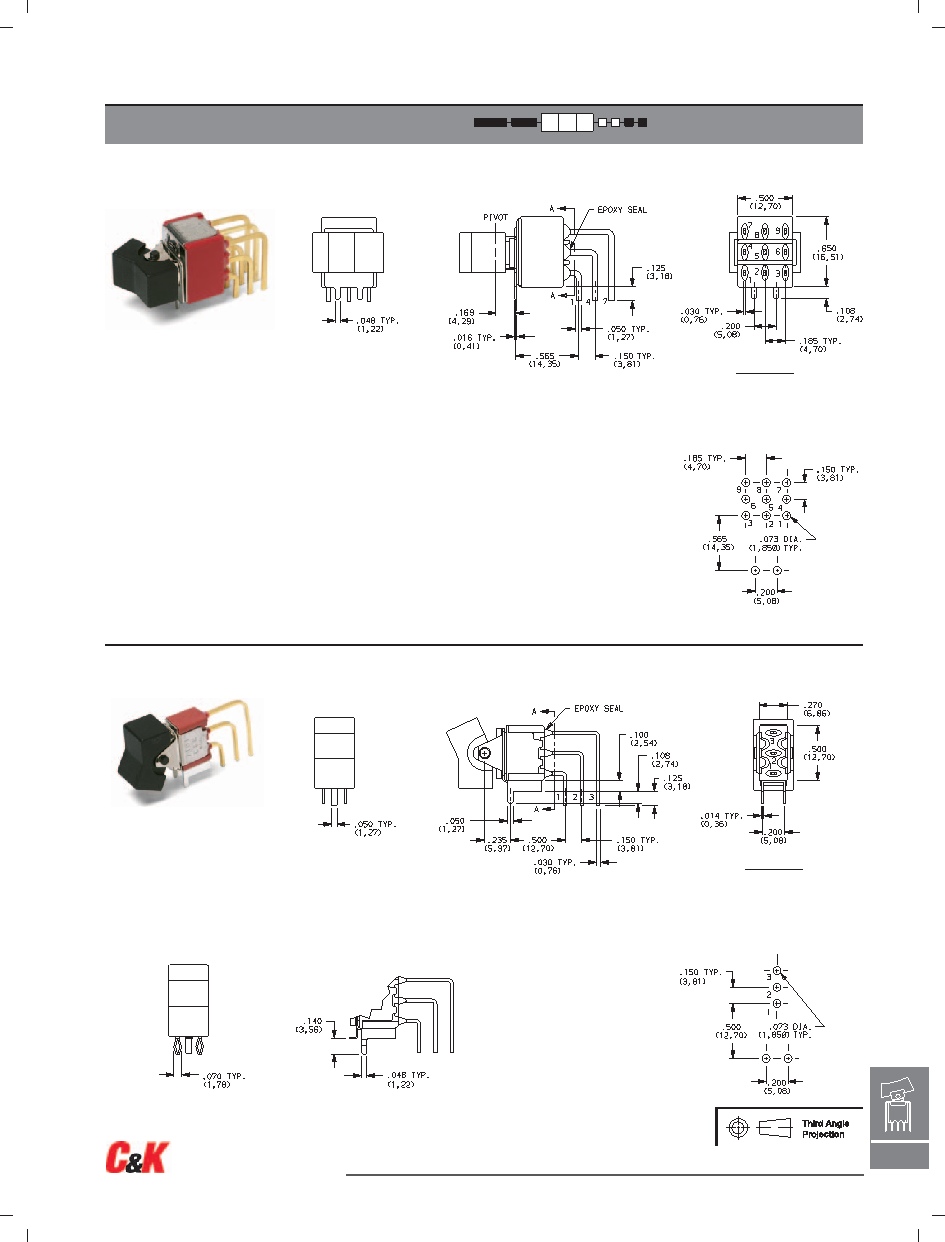

TERMINATIONS

7000 Series

Miniature Rocker & Lever Handle Switches

Actuator Shown In Pos. 1

SECTION A-A

PC MOUNTING

Actuator Shown In Pos. 1

SECTION A-A

PC MOUNTING

AV3

VERTICAL RIGHT ANGLE, SNAP-IN, PC THRU-HOLE,

.150" PITCH

AV2

VERTICAL RIGHT ANGLE, PC THRU-HOLE,

.150" PITCH

A

RIGHT ANGLE, PC THRU-HOLE

Not available with I seal option. Available actuators, see pages H-7 and H-13.

Terminal bend radii and lead-in manufacturing option.

Not available with I seal option. Available actuators, see pages H-7 and H-13.

Terminal bend radii and lead-in manufacturing option.

7301J1ABE2

Horizontal Actuation

3PDT

7101J1AV2BE2

Vertical Actuation

SPDT

H–15

H

Rocker

Dimensions are shown: Inch (mm)

Specifications and dimensions subject to change

www.ck-components.com

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7303J11CSI11 | ROCKER SWITCH, 3PDT, LATCHED, 5A, 28VDC, THROUGH HOLE-STRAIGHT |

| 7213J52Z3GI11 | ROCKER SWITCH, DPDT, LATCHED AND MOMENTARY, 5A, 28VDC, PANEL MOUNT |

| 7213J8AV2PE3 | ROCKER SWITCH, DPDT, LATCHED AND MOMENTARY, 0.02A, 20VDC, THROUGH HOLE-RIGHT ANGLE |

| 7213J8AV2RE3 | ROCKER SWITCH, DPDT, LATCHED AND MOMENTARY, 5A, 28VDC, THROUGH HOLE-RIGHT ANGLE |

| 7215J15W3PE3 | ROCKER SWITCH, DPDT, MOMENTARY, 0.02A, 20VDC, PANEL MOUNT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 7303J11Z3QE22 | 功能描述:搖臂開關(guān)與扳鈕開關(guān) Rocker RoHS:否 制造商:C&K Components 觸點形式: 開關(guān)功能: 電流額定值:50 mA 電壓額定值 AC: 電壓額定值 DC:30 V 功率額定值: 端接類型: 執(zhí)行器:Paddle 顏色: 安裝風(fēng)格:Panel 端子密封: 觸點電鍍: 照明:Not Illuminated 照明顏色: |

| 7303J11Z3QE32 | 功能描述:搖臂開關(guān)與扳鈕開關(guān) RoHS:否 制造商:C&K Components 觸點形式: 開關(guān)功能: 電流額定值:50 mA 電壓額定值 AC: 電壓額定值 DC:30 V 功率額定值: 端接類型: 執(zhí)行器:Paddle 顏色: 安裝風(fēng)格:Panel 端子密封: 觸點電鍍: 照明:Not Illuminated 照明顏色: |

| 7303J11ZBE22 | 功能描述:搖臂開關(guān)與扳鈕開關(guān) RoHS:否 制造商:C&K Components 觸點形式: 開關(guān)功能: 電流額定值:50 mA 電壓額定值 AC: 電壓額定值 DC:30 V 功率額定值: 端接類型: 執(zhí)行器:Paddle 顏色: 安裝風(fēng)格:Panel 端子密封: 觸點電鍍: 照明:Not Illuminated 照明顏色: |

| 7303J11ZGE22 | 功能描述:搖臂開關(guān)與扳鈕開關(guān) RoHS:否 制造商:C&K Components 觸點形式: 開關(guān)功能: 電流額定值:50 mA 電壓額定值 AC: 電壓額定值 DC:30 V 功率額定值: 端接類型: 執(zhí)行器:Paddle 顏色: 安裝風(fēng)格:Panel 端子密封: 觸點電鍍: 照明:Not Illuminated 照明顏色: |

| 7303J11ZQE22 | 功能描述:搖臂開關(guān)與扳鈕開關(guān) ON OFF ON 3PDT 5A 250VAC 28VDC RoHS:否 制造商:C&K Components 觸點形式: 開關(guān)功能: 電流額定值:50 mA 電壓額定值 AC: 電壓額定值 DC:30 V 功率額定值: 端接類型: 執(zhí)行器:Paddle 顏色: 安裝風(fēng)格:Panel 端子密封: 觸點電鍍: 照明:Not Illuminated 照明顏色: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。