- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371197 > X24022SM-3 Serial E2PROM PDF資料下載

參數(shù)資料

| 型號: | X24022SM-3 |

| 英文描述: | Serial E2PROM |

| 中文描述: | 串行E2PROM |

| 文件頁數(shù): | 7/14頁 |

| 文件大小: | 58K |

| 代理商: | X24022SM-3 |

X24022

7

BUS ACTIVITY:

MASTER

SDA LINE

BUS ACTIVITY:

X24022

S

T

A

R

T

SLAVE

ADDRESS

S

S

T

O

P

P

A

C

K

A

C

K

A

C

K

WORD

ADDRESS n

SLAVE

ADDRESS

DATA n

S

T

A

R

T

S

BUS ACTIVITY:

MASTER

SDA LINE

BUS ACTIVITY:

X24022

S

T

A

R

T

SLAVE

ADDRESS

S

S

T

O

P

P

A

C

K

DATA

READ OPERATIONS

Read operations are initiated in the same manner as

write operations with the exception that the R/

W

bit of the

slave address is set to a one. There are three basic read

operations: current address read, random read and

sequential read.

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read

operation, the master must either issue a stop condition

during the ninth cycle or hold SDA HIGH during the ninth

clock cycle and then issue a stop condition.

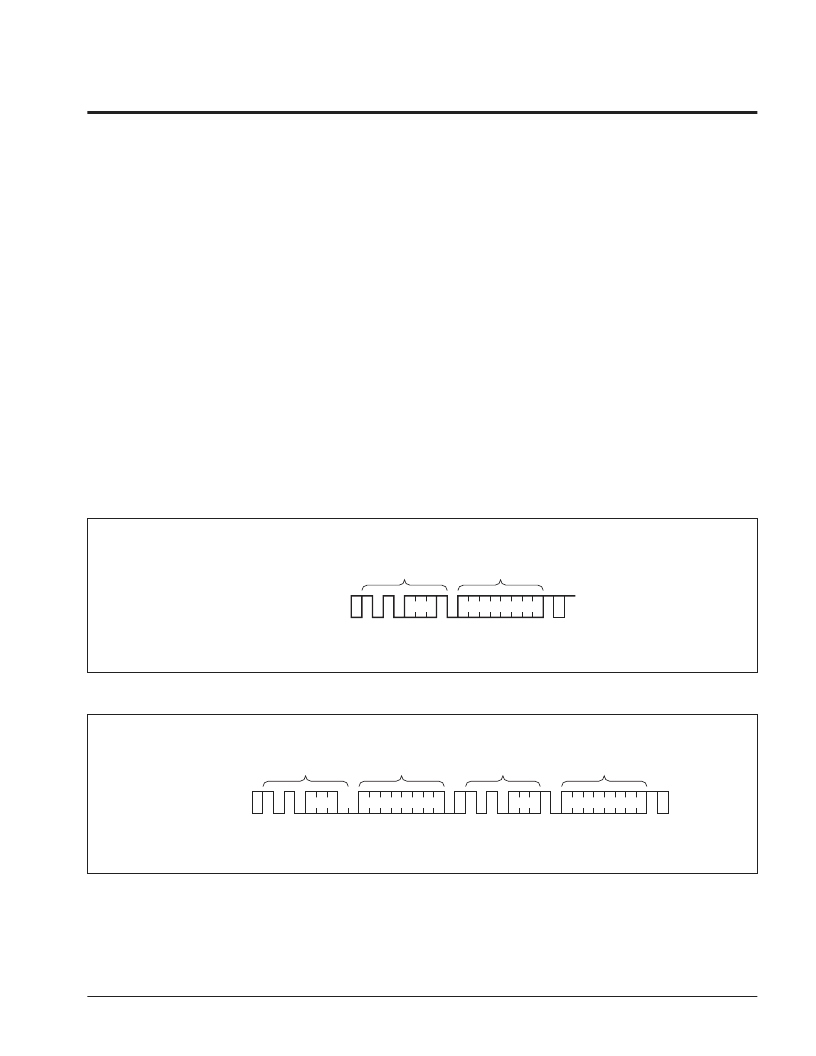

Current Address Read

Internally the X24022 contains an address counter that

incremented by one. Therefore, if the last access (either

a read or write) was to address n, the next read operation

would access data from address n + 1. Upon receipt of

the slave address with R/

W

set to one, the X24022

issues an acknowledge and transmits the eight bit word

during the next eight clock cycles. The read operation is

terminated by the master; by not responding with an

acknowledge and by issuing a stop condition. Refer to

Figure 7 for the sequence of address, acknowledge and

data transfer.

Random Read

Random read operations allow the master to access any

memory location in a random manner. Prior to issuing

the slave address with the R/

W

bit set to one, the master

must first perform a “dummy” write operation. The mas-

ter issues the start condition, and the slave address

followed by the word address it is to read. After the word

address acknowledge, the master immediately reissues

the start condition and the slave address with the R/

W

bit

set to one. This will be followed by an acknowledge from

the X24022 and then by the eight bit word. The read

operation is terminated by the master; by not responding

with an acknowledge and by issuing a stop condition.

Refer to Figure 8 for the address, acknowledge and data

transfer sequence.

Figure 7. Current Address Read

3848 FHD F13

Figure 8. Random Read

3848 FHD F14

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X24022PI | Controller IC; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No |

| X24022PI-3 | Controller IC; Leaded Process Compatible:Yes; Peak Reflow Compatible (260 C):Yes |

| X24022PM | IC SYNC STEP DOWN CTRLR 28-TSSOP |

| X24022S | Serial E2PROM |

| X24022S-2.7 | Controller IC; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No RoHS Compliant: No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X24026 | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:Serial E2PROM |

| X24026H | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:Serial E2PROM |

| X24026H-2.7 | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:Serial E2PROM |

| X24026T20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| X24026T20-2.7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。