- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄193533 > SMX55161A-80HKCI (AUSTIN SEMICONDUCTOR INC) 256K X 16 VIDEO DRAM, 80 ns, CDFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | SMX55161A-80HKCI |

| 廠商: | AUSTIN SEMICONDUCTOR INC |

| 元件分類: | DRAM |

| 英文描述: | 256K X 16 VIDEO DRAM, 80 ns, CDFP64 |

| 封裝: | CERAMIC, FP-64 |

| 文件頁(yè)數(shù): | 45/64頁(yè) |

| 文件大小: | 1223K |

| 代理商: | SMX55161A-80HKCI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)當(dāng)前第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

VRAM

SM55161A

Production

Austin Semiconductor, Inc.

AustinSemiconductor,Inc.reservestherighttochangeproductsorspecificationswithoutnotice.

5

SMJ55161A

Rev. 1.6

03/05

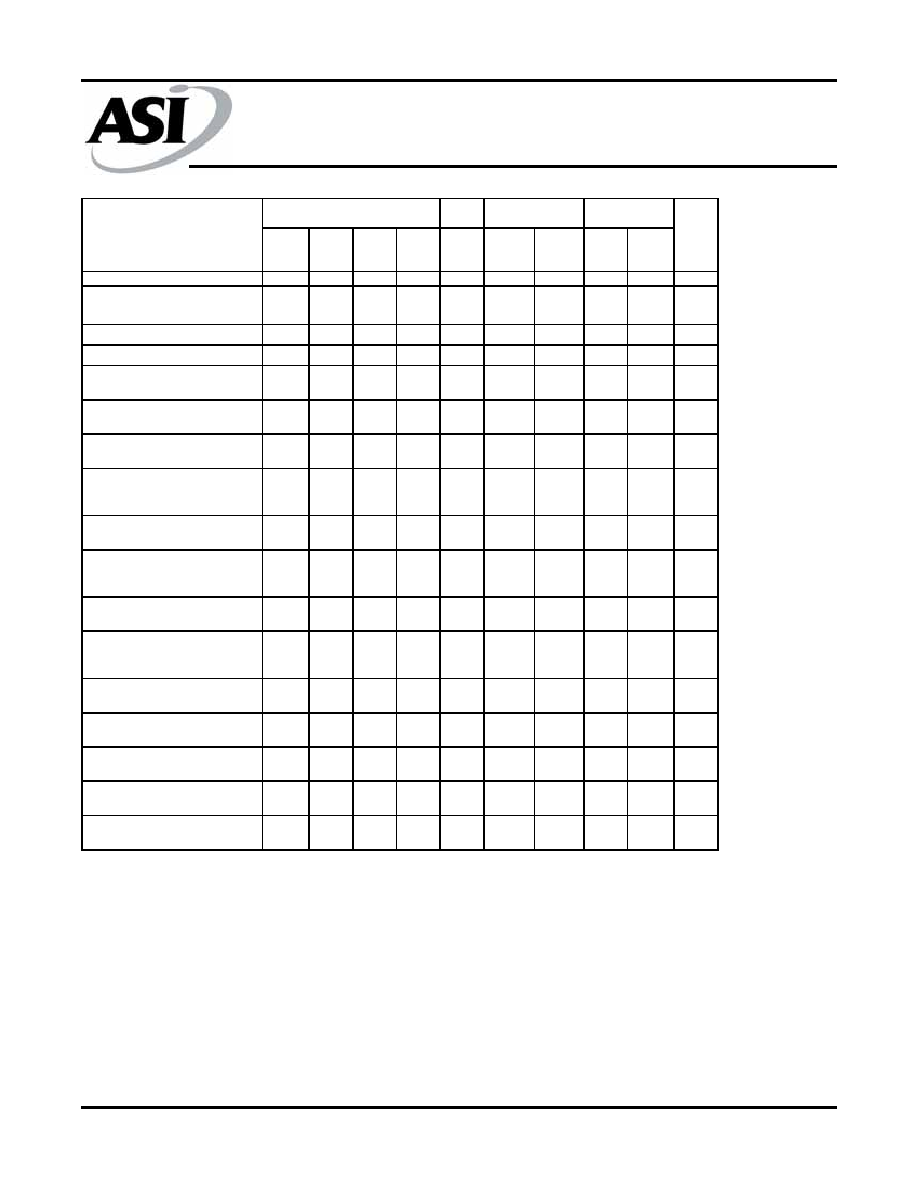

TABLE 1: DRAM & SAM FUNCTIONS

CASx\

FALL

CASx\

2

TRG\

WE\

DSF

RAS\

CASX\

3

RAS\

CASL\

CASU\

WE\

Reserved (do not use)

L

X

---

CBR refresh (no reset) and stop-

point set

4

LX

L

H

X

Stop

point

5

X

CBRS

CBR refresh (option reset)

6

L

X

H

L

X

CBR

CBR refresh (no reset)

7

L

X

H

X

CBRN

Full-register-transfer read

H

L

H

L

X

Row

Address

Tap

Point

XX

RT

Split-register-transfer read

H

L

H

X

Row

Address

Tap

Point

X

SRT

DRAM write

(nonpersistent write-per-bit)

H

LLL

Row

Address

Column

Address

Write

Mask

Valid

Data

RWM

DRAM block write

(nonpersistent write-per-bit)

HH

L

H

Row

Address

Block

Address

A3-A8

Write

Mask

Column

Mask

BWM

DRAM write

(persistent write-per-bit)

H

LLL

Row

Address

Column

Address

X

Valid

Data

RWM

DRAM block write

(persistent write-per-bit)

HH

L

H

Row

Address

Block

Address

A3-A8

X

Column

Mask

BWM

DRAM write (nonmasked)

H

L

Row

Address

Column

Address

X

Valid

Data

RW

DRAM block write (nonmasked)

H

L

H

Row

Address

Block

Address

A3-A8

X

Column

Mask

BW

Load write-mask register

8

H

HHH

L

Refresh

Address

XX

Write

Mask

LMR

Load color register

H

HHHH

Refresh

Address

XX

Color

Data

LCR

Masked Write Transfer

9

H

LLL

X

Row

Address

Tap

Point

Write

Mask

X

MWT

Masked Split Write Transfer

9

HL

L

H

X

Row

Address

Tap

Point

Write

Mask

X

MSWT

Masked Flash Write Transfer

9

HH

L

H

X

Row

Address

X

Write

Mask

---

FWM

MNE

CODE

FUNCTION

RAS\ FALL

ADDRESS

DQ0-DQ15

1

LEGEND:

Col Mask = H: Write to address/column enabled

Write Mask = H: Write to I/O enabled

X = Don’t Care

NOTES:

1. DQ0–DQ15 are latched on either the first falling edge of CASx\ or the falling edge of WE\, whichever occurs later.

2. Logic L is selected when either or both CASL\ and CASU\ are low.

3. The column address and block address are latched on the first falling edge of CASx\.

4. CBRS cycle should be performed immediately after the power-up initialization cycle.

5. A0–A3, A8: don’t care; A4–A7: stop-point code

6. CBR refresh (option reset) mode ends persistent write-per-bit mode and stop-point mode.

7. CBR refresh (no reset) mode does not end persistent write-per-bit mode or stop-point mode.

8. Load-write-mask-register cycle sets the persistent write-per-bit mode. The persistent write-per-bit mode is reset only by the CBR (option

reset) cycle.

9. MWT, MSWT, FWM function shown are for nonpersistent mask writes. These functions also support persistent mask write.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN1767K | PANEL MOUNT, CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP |

| SN2297K | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP |

| SN54ALS15J-00 | ALS SERIES, TRIPLE 3-INPUT AND GATE, CDIP14 |

| SN54ALS240AFK | ALS SERIES, DUAL 4-BIT DRIVER, INVERTED OUTPUT, CQCC20 |

| SN54HC393W | HC/UH SERIES, ASYN NEGATIVE EDGE TRIGGERED 4-BIT UP BINARY COUNTER, CDFP14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SMX55161A-80HKCM | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:262144 x 16 BIT VRAM MULTIPORT VIDEO RAM |

| SMX55234W | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| SMX55C105KAN240 | 功能描述:多層陶瓷電容器MLCC - 含引線 50volts 1uF 10% X7R High Temp RoHS:否 制造商:AVX 電容:470 pF 容差:10 % 電壓額定值:3 kV 端接類型:Radial 工作溫度范圍: 溫度系數(shù)/代碼:X7R 引線間隔:5.08 mm 產(chǎn)品:Automotive MLCCs 引線類型: |

| SMX57A392KAN120 | 制造商:AVX Corporation 功能描述:CAP HIGH TEMP .0039UF 500V NPO 10% +200C 3LEADS/SIDE - Bulk |

| SMX-5F-QA | 制造商:QUARTZCOM 制造商全稱:QUARTZCOM the communications company 功能描述:Low profile SMD Crystal Pin compatible to several plastic moulded Crystals |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。