μ

PD30500, 30500A, 30500B

14

Data Sheet U12031EJ4V0DS00

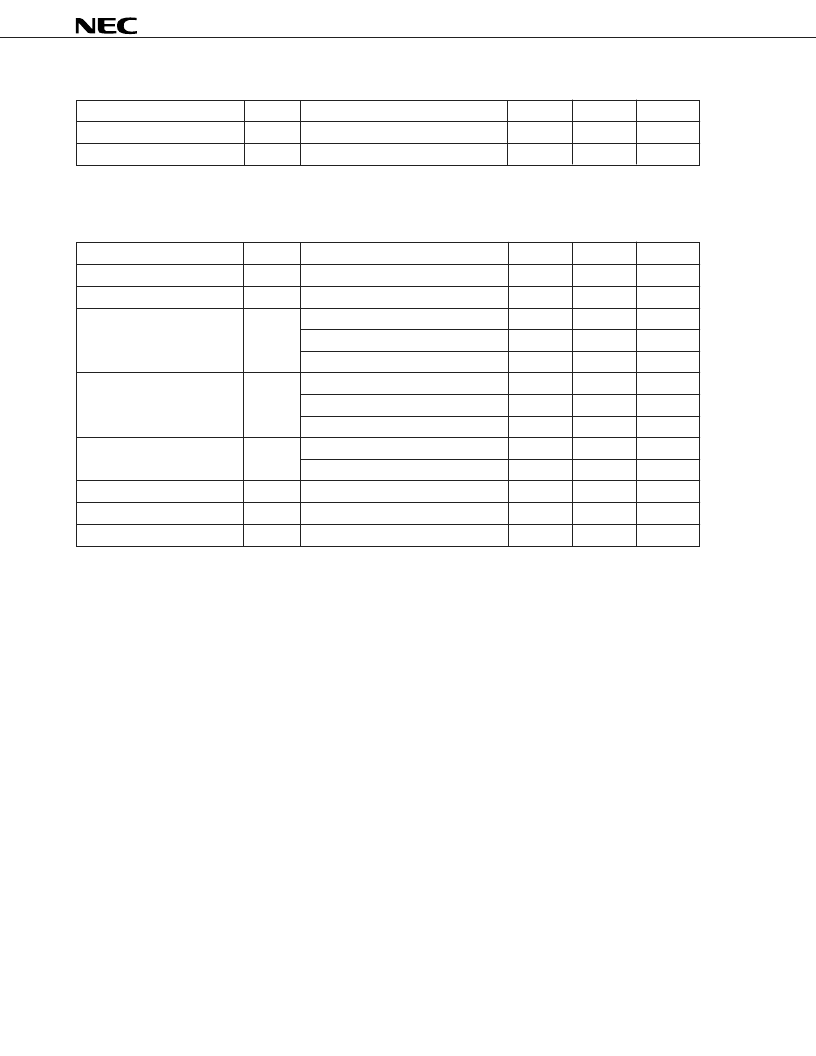

Capacitance

Parameter

Symbol

Condition

MIN.

MAX.

Unit

Input capacitance

C

In

5

pF

Output capacitance

C

out

7

pF

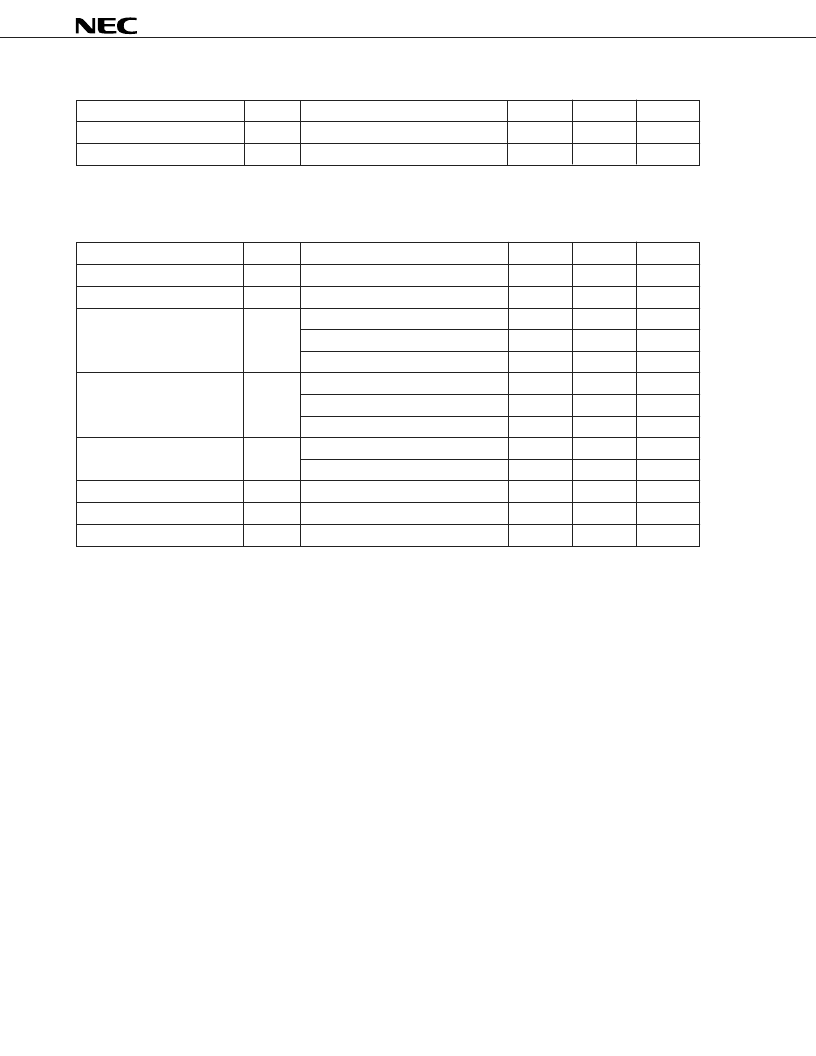

AC Characteristics (T

C

= 0 to +70

°

C (PGA Package), T

C

= 0 to +85

°

C (BGA Package), V

DD

= 3.3 V

±

5%)

Clock parameter

Parameter

Symbol

Condition

MIN.

MAX.

Unit

System clock high-level width

t

CH

3.0

ns

System clock low-level width

t

CL

3.0

ns

System clock frequency

Notes 1, 2

150 MHz

20

75

MHz

180 MHz

20

90

MHz

200 MHz

20

100

MHz

System clock cycle

t

CP

150 MHz

13.3

50

ns

180 MHz

11.1

50

ns

200 MHz

10

50

ns

System clock jitter

t

ji

System clock frequency > 66 MHz

±

125

ps

System clock frequency

≤

66 MHz

±

250

ps

System clock rise time

t

CR

2.0

ns

System clock fall time

t

CF

2.0

ns

Mode clock cycle

t

MOC

256

×

t

CP

ns

Notes 1.

The operation of the V

R

5000 is guaranteed only when the PLL is operating

2.

The operation is guaranteed if the internal operating frequency 100 MHz or higher.