- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382783 > μPD30700L (NEC Corp.) 64-Bit Microprocessor(64位RISC微處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | μPD30700L |

| 廠商: | NEC Corp. |

| 英文描述: | 64-Bit Microprocessor(64位RISC微處理器) |

| 中文描述: | 64位微處理器(64位的RISC微處理器) |

| 文件頁數(shù): | 11/36頁 |

| 文件大小: | 210K |

| 代理商: | ΜPD30700L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

μ

PD30500, 30500A, 30500B

11

Data Sheet U12031EJ4V0DS00

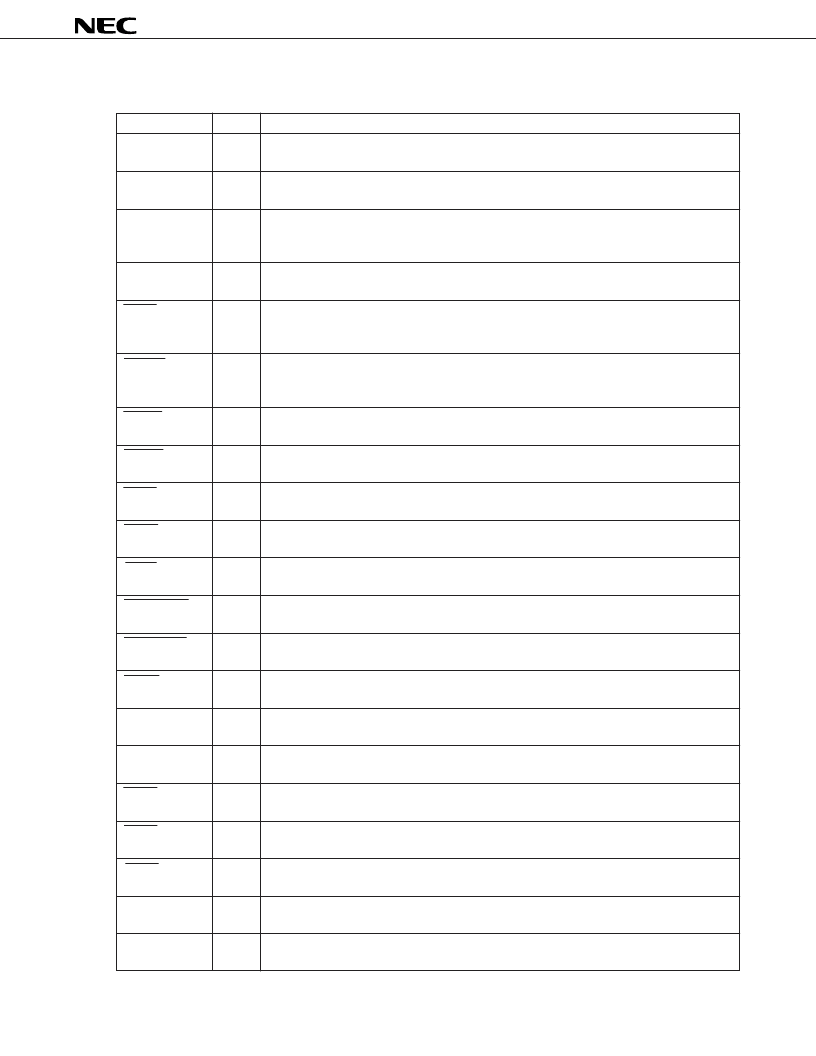

1. PIN FUNCTIONS

Pin Name

I/O

Function

SysAD (0:63)

I/O

System address/data bus.

64-bit bus for communication between processor, secondary cache and external agent.

SysADC (0:7)

I/O

System address/data check bus.

8-bit bus including check bits for the SysAD bus.

SysCmd (0:8)

I/O

System command/data ID bus.

9-bit bus for communication of commands and data identifiers between processor

and external agent.

SysCmdP

I/O

System command/data ID bus parity.

1-bit even number parity bit for the SysCmd bus.

ValidIn

Input

Valid in.

Signal indicating that external agent has transmitted valid address or data onto

SysAD bus and valid command or data identifier onto SysCmd bus.

ValidOut

Output

Valid out.

Signal indicating that processor has transmitted valid address or data onto SysAD

bus and valid command or data identifier onto SysCmd bus.

ExtRqst

Input

External request.

Signal used by external agent to request for its use by system interface.

Release

Output

Interface release.

Signal indicating that the processor has released the system interface to the slave state.

WrRdy

Output

Write ready.

Signal indicating that the external agent can accept a processor write request.

RdRdy

Input

Read ready.

Signal indicating that external agent can accept a processor read request.

ScCLR

Output

Secondary cache block clear.

Clears all the valid bits of the tag RAM.

ScCWE (0:1)

Output

Secondary cache write enable.

Write enable signal for the secondary cache RAM.

ScDCE (0:1)

Output

Data RAM chip select.

Chip select signal for secondary cache RAM.

ScDOE

Input

Data RAM output enable.

Data output enable signal from the external agent.

ScLine (0:15)

Output

Secondary cache line index.

Cache line index output of the secondary cache.

ScMatch

Input

Secondary cache tag match.

Tag match signal from secondary cache tag RAM.

ScTCE

Output

Secondary cache tag RAM chip select.

Chip select signal of the secondary cache tag RAM.

ScTDE

Output

Secondary cache tag RAM data enable.

Data enable signal from the secondary cache tag RAM.

ScTOE

Output

Secondary cache tag RAM output enable.

Output enable signal from the secondary cache tag RAM.

ScWord (0:1)

I/O

Secondary cache word index.

Signal indicating that the double word of the secondary cache index is correct.

ScValid

I/O

Secondary cache valid.

Signal indicating that the data of the secondary cache is valid.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD30700 | 64-Bit Microprocessor(64位RISC微處理器) |

| μPD30710 | 64-Bit Microprocessor(64位RISC微處理器) |

| μPD431000A-X | 1 M-Bit CMOS Static RAM(1M CMOS靜態(tài)RAM) |

| μPD431008 | 1M-Bit CMOS Fast Static RAM(1M位CMOS 快速靜態(tài)) |

| μPD431016 | 1M-Bit CMOS Fast Static RAM(1M位CMOS 快速靜態(tài)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD308 | 制造商:NIEC 制造商全稱:Nihon Inter Electronics Corporation 功能描述:DIODE MODULE 30A/800V |

| PD30-CADG13 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Single Digit 7 Segment 4.0” LED Display |

| PD30-CADO12 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Single Digit 7 Segment 4.0” LED Display |

| PD30-CADR09 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Single Digit 7 Segment 4.0” LED Display |

| PD30-CADR21 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Single Digit 7 Segment 4.0” LED Display |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。