- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371392 > 24AA080-ISN (Microchip Technology Inc.) 8K/16K 1.8V SPI Bus Serial EEPROM PDF資料下載

參數(shù)資料

| 型號: | 24AA080-ISN |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | 8K/16K 1.8V SPI Bus Serial EEPROM |

| 中文描述: | 8K/16K 1.8V的SPI總線串行EEPROM |

| 文件頁數(shù): | 7/12頁 |

| 文件大小: | 92K |

| 代理商: | 24AA080-ISN |

1996 Microchip Technology Inc.

Preliminary

DS21146D-page 7

25AA080/160

2.3

Write Status Register (WRSR)

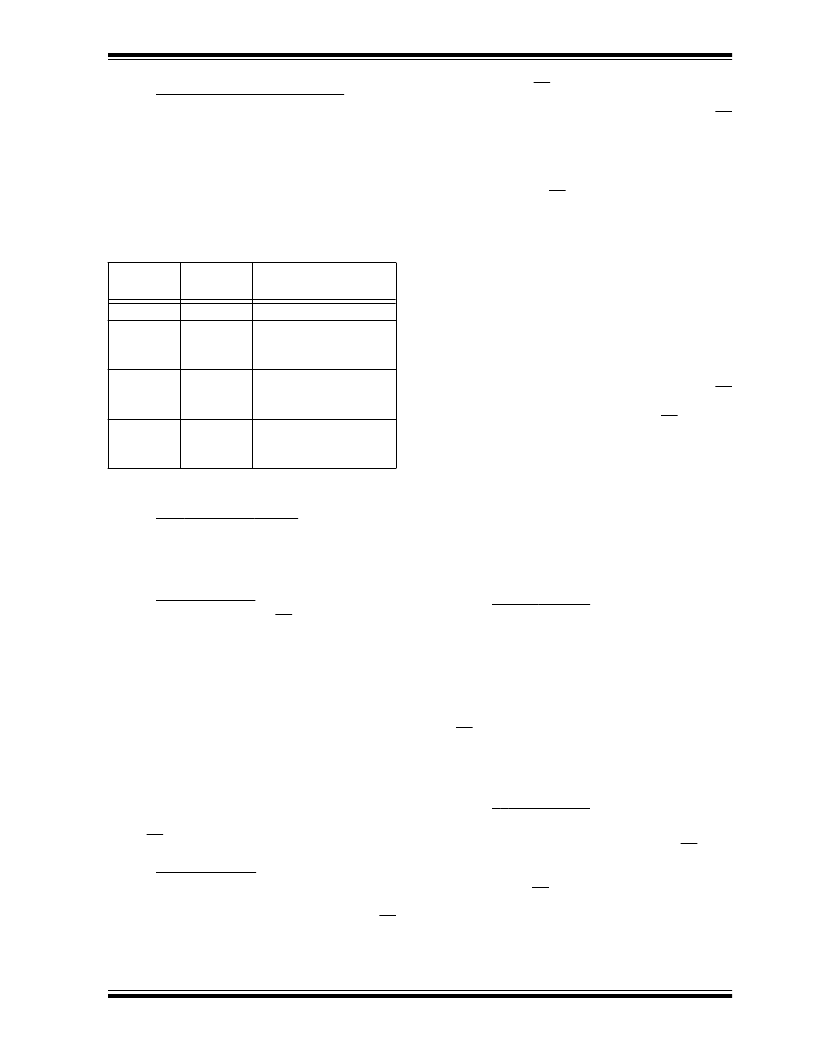

The WRSR instruction allows the user to select one of

four protection options for the array by writing to the

appropriate bits in the status register. The array is

divided up into four segments. The user has the ability

to write protect none, one, two, or all four of the seg-

ments of the array. The partitioning is controlled as illus-

trated in table below.

See Figure 3-6 for WRSR timing sequence.

TABLE 2-3:

ARRAY PROTECTION

3.0

DEVICE OPERATION

3.1

Clock and Data Timing

Data input on the SI pin is latched on the rising edge of

SCK. Data is output on the SO pin after the falling edge

of SCK.

3.2

Read Sequence

The part is selected by pulling CS low. The 8-bit read

instruction is transmitted to the 25AA080/160 followed

by the 16-bit address, with the five (25AA160) or six

(25AA080) MSBs of the address being don’t care bits.

After the correct read instruction and address are sent,

the data stored in the memory at the selected address

is shifted out on the SO pin. The data stored in the

memory at the next address can be read sequentially

by continuing to provide clock pulses. The internal

address pointer is automatically incremented to the

next higher address after each byte of data is shifted

out. When the highest address is reached ($3FF for

25AA080, $7FF for 25AA160) the address counter rolls

over to address $000 allowing the read cycle to be con-

tinued indefinitely. The read operation is terminated by

setting CS high (see Figure 3-1).

3.3

Write Sequence

Prior to any attempt to write data to the 25AA080/160,

the write enable latch must be set by issuing the WREN

instruction (see Figure 3-2). This is done by setting CS

low and then clocking the proper instruction into the

25AA080/160. After all eight bits of the instruction are

BP1

BP0

Array Addresses

Write Protected

0

0

0

1

none

upper 1/4

300h-3FFh for 25AA080

600h-7FFh for 25AA160

upper 1/2

200h-3FFh for 25AA080

400h-7FFh for 25AA160

all

000h-3FFh for 25AA080

000h-7FFh for 25AA160

1

0

1

1

transmitted, the CS must be brought high to set the

write enable latch. If the write operation is initiated

immediately after the WREN instruction without CS

being brought high, the data will not be written to the

array because the write enable latch will not have been

properly set.

Once the write enable latch is set, the user may pro-

ceed by setting the CS low, issuing a write instruction,

followed by the 16-bit address, with the five (25AA080)

or six (25AA080) MSBs of the address being don’t care

bits, and then the data to be written. Up to 16 bytes of

data can be sent to the 25AA080/160 before a write

cycle is necessary. The only restriction is that all of the

bytes must reside in the same page. A page address

begins with XXXX XXXX XXXX 0000 and ends with

XXXX XXXX XXXX 1111. If the internal address

counter reaches XXXX XXXX XXXX 1111 and the

clock continues, the counter will roll back to the first

address of the page and overwrite any data in the page

that may have been written.

For the data to be actually written to the array, the CS

must be brought high after the least significant bit (D0)

of the n

th

data byte has been clocked in. If CS is brought

high at any other time, the write operation will not be

completed. See Figure 3-3 and Figure 3-4 for more

detailed illustrations on the byte write sequence and the

page write sequence, respectively.

While the write is in progress, the status register may

be read to check the status of the WPEN, WIP, WEL,

BP1, and BP0 bits. A read attempt of a memory array

location will not be possible during a write cycle. When

a write cycle is completed, the write enable latch is

reset.

3.4

Data Protection

The following protection has been implemented to pre-

vent inadvertent writes to the array:

The write enable latch is reset on power-up.

A write enable instruction must be issued to set

the write enable latch.

After a successful byte write, page write, or status

register write, the write enable latch is reset.

CS must be set high after the proper number of

clock cycles to start an internal write cycle.

Access to the array during an internal write cycle

is ignored and programming is continued.

3.5

Power On State

The 25AA080/160 powers on in the following state:

The device is in low power standby mode (CS=1).

The write enable latch is reset.

SO is in high impedance state.

A low level on CS is required to enter active state.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24AA080-P | 8K/16K 1.8V SPI Bus Serial EEPROM |

| 24AA080-SN | 8K/16K 1.8V SPI Bus Serial EEPROM |

| 24AA160-SN | 8K/16K 1.8V SPI Bus Serial EEPROM |

| 24AA160-P | 8K/16K 1.8V SPI Bus Serial EEPROM |

| 24AA164TSN | 16K 1.8V Cascadable I2CTM Serial EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24AA080-P | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:8K/16K 1.8V SPI Bus Serial EEPROM |

| 24AA080-SN | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:8K/16K 1.8V SPI Bus Serial EEPROM |

| 24AA081 | 功能描述:整流器/與可變電容器 NO COLOR 2.8-12.5PFD RoHS:否 制造商:Xicon 電容范圍:2.8 pF to 12.5 pF 容差: 電壓額定值:200 V 工作溫度范圍:- 35 C to + 85 C 端接類型:SMD/SMT 產(chǎn)品:Trimmer Capacitors - Ceramic Dielectric |

| 24AA082 | 功能描述:整流器/與可變電容器 BLUE 3.5-20 PFD RoHS:否 制造商:Xicon 電容范圍:2.8 pF to 12.5 pF 容差: 電壓額定值:200 V 工作溫度范圍:- 35 C to + 85 C 端接類型:SMD/SMT 產(chǎn)品:Trimmer Capacitors - Ceramic Dielectric |

| 24AA083 | 功能描述:整流器/與可變電容器 YELLOW 5.0-30PFD RoHS:否 制造商:Xicon 電容范圍:2.8 pF to 12.5 pF 容差: 電壓額定值:200 V 工作溫度范圍:- 35 C to + 85 C 端接類型:SMD/SMT 產(chǎn)品:Trimmer Capacitors - Ceramic Dielectric |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。