- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371394 > 24C02B-ESN (Microchip Technology Inc.) 1K/2K 5.0V I 2 C ⑩ Serial EEPROM PDF資料下載

參數(shù)資料

| 型號: | 24C02B-ESN |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | 1K/2K 5.0V I 2 C ⑩ Serial EEPROM |

| 中文描述: | 1K/2K 5.0VI 2葷⑩串行EEPROM |

| 文件頁數(shù): | 5/12頁 |

| 文件大小: | 162K |

| 代理商: | 24C02B-ESN |

24C01B/02B

1997 Microchip Technology Inc.

Preliminary

DS21233A-page 5

3.6

Device Address

After generating a START condition, the bus master

transmits the slave address consisting of a 4-bit device

code (1010) for the 24C01B/02B, followed by three

don't care bits.

The eighth bit of slave address determines if the master

device wants to read or write to the 24C01B/02B

(Figure 3-2).

The 24C01B/02B monitors the bus for its correspond-

ing slave address all the time. It generates an acknowl-

edge bit if the slave address was true and it is not in a

programming mode.

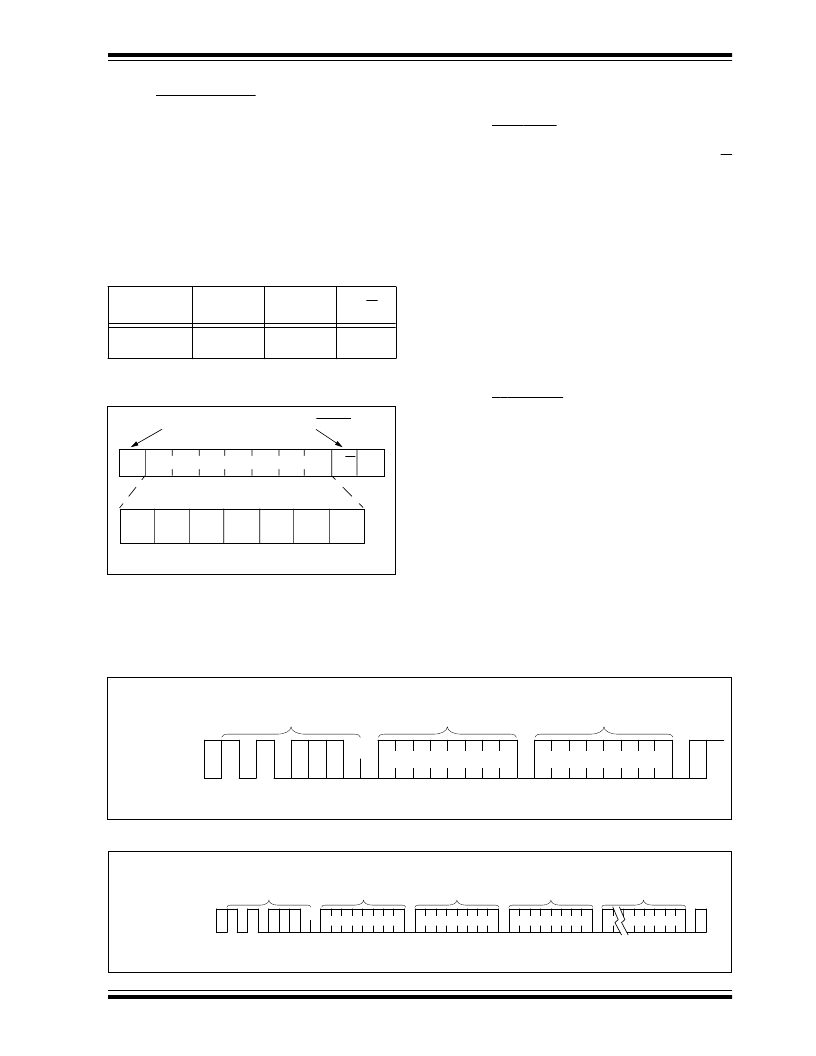

FIGURE 3-2:

CONTROL BYTE

ALLOCATION

4.0

WRITE OPERATION

4.1

Byte Write

Following the start signal from the master, the device

code (4 bits), the don't care bits (3 bits), and the R/W

bit which is a logic low is placed onto the bus by the

master transmitter. This indicates to the addressed

slave receiver that a byte with a word address will follow

after it has generated an acknowledge bit during the

ninth clock cycle. Therefore the next byte transmitted

by the master is the word address and will be written

into the address pointer of the 24C01B/02B. After

receiving another acknowledge signal from the

24C01B/02B the master device will transmit the data

word to be written into the addressed memory location.

The 24C01B/02B acknowledges again and the master

generates a stop condition. This initiates the internal

write cycle, and during this time the 24C01B/02B will

not generate acknowledge signals (Figure 4-1).

4.2

Page Write

The write control byte, word address and the first data

byte are transmitted to the 24C01B/02B in the same

way as in a byte write. But instead of generating a stop

condition the master transmits up to eight data bytes to

the 24C01B/02B which are temporarily stored in the

on-chip page buffer and will be written into the memory

after the master has transmitted a stop condition. After

the receipt of each word, the three lower order address

pointer bits are internally incremented by one. The

higher order five bits of the word address remains con-

stant. If the master should transmit more than eight

words prior to generating the stop condition, the

address counter will roll over and the previously

received data will be overwritten. As with the byte write

operation, once the stop condition is received an inter-

nal write cycle will begin (Figure 4-2).

FIGURE 4-1:

BYTE WRITE

FIGURE 4-2:

PAGE WRITE

Operation

Control

Code

Chip

Select

R/W

Read

Write

1010

1010

XXX

XXX

1

0

X = Don’t care

R/W

A

1

0

1

0

X

X

X

READ/WRITE

START

SLAVE ADDRESS

S

P

S

T

A

R

T

S

T

O

P

BUS ACTIVITY

MASTER

SDA LINE

BUS ACTIVITY

A

C

K

A

C

K

A

C

K

CONTROL

BYTE

WORD

ADDRESS

DATA

S

P

BUS ACTIVITY

MASTER

SDA LINE

BUS ACTIVITY

S

T

A

R

T

S

T

O

P

CONTROL

BYTE

WORD

ADDRESS (n)

DATA n

DATAn + 7

DATAn + 1

A

C

K

A

C

K

A

C

K

A

C

K

A

C

K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24C01C | 1K 5.0V I 2 C ⑩ Serial EEPROM |

| 24C01C-IP | 1K 5.0V I 2 C ⑩ Serial EEPROM |

| 24C01C-ISN | 1K 5.0V I 2 C ⑩ Serial EEPROM |

| 24C01C-IST | IC, QUAD PHY 10GX |

| 24C01C-P | 1K 5.0V I 2 C ⑩ Serial EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24C02BT-E/P | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:1K/2K 5.0V I2C⑩ Serial EEPROM |

| 24C02BT-E/SN | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:1K/2K 5.0V I2C⑩ Serial EEPROM |

| 24C02C | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:2K 5.0V I 2 C ⑩ Serial EEPROM |

| 24C02C/P | 功能描述:電可擦除可編程只讀存儲器 256x8 RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| 24C02C/P | 制造商:Microchip Technology Inc 功能描述:IC EEPROM SERIAL 2K |

發(fā)布緊急采購,3分鐘左右您將得到回復。