- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371396 > 24C65-IP (Microchip Technology Inc.) 64K 5.0V I 2 C Smart Serial EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | 24C65-IP |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | 64K 5.0V I 2 C Smart Serial EEPROM |

| 中文描述: | 64K的5.0VI 2葷智能串行EEPROM |

| 文件頁數(shù): | 8/16頁 |

| 文件大小: | 120K |

| 代理商: | 24C65-IP |

24C65

DS21058G-page 8

1996 Microchip Technology Inc.

define the number of blocks to be write protected. For

example, if three blocks are to be protected, the third

byte would be 10XX0011. After the third byte is sent to

the device, it will acknowledge and a STOP bit is then

sent by the master to complete the command.

During a normal write sequence, if an attempt is made

to write to a protected address, no data will be written

and the device will not report an error or abort the com-

mand. If a write command is attempted across a

secure boundary, unprotected addresses will be written

and protected addresses will not.

5.8

Security Configuration Read

The status of the secure portion of memory can be read

by using the same technique as programming this

option except the READ bit (bit 6) of the configuration

byte is set to a one. After the configuration byte is sent,

the device will acknowledge and then send two bytes of

data to the master just as in a normal read sequence.

The master must acknowledge the first byte and not

acknowledge the second, and then send a stop bit to

end the sequence. The upper four bits of both of these

bytes will always be read as '1's. The lower four bits of

the first byte contains the starting secure block. The

lower four bits of the second byte contains the number

of secure blocks. The default starting secure block is fif-

teen and the default number of secure blocks is zero

(Figure 8-1).

6.0

ACKNOWLEDGE POLLING

Since the device will not acknowledge during a write

cycle, this can be used to determine when the cycle is

complete (this feature can be used to maximize bus

throughput). Once the stop condition for a write com-

mand has been issued from the master, the device ini-

tiates the internally timed write cycle. ACK polling can

be initiated immediately. This involves the master send-

ing a start condition followed by the control byte for a

write command (R/W = 0). If the device is still busy with

the write cycle, then no ACK will be returned. If the

cycle is complete, then the device will return the ACK

and the master can then proceed with the next read or

write command. See Figure 6-1 for flow diagram.

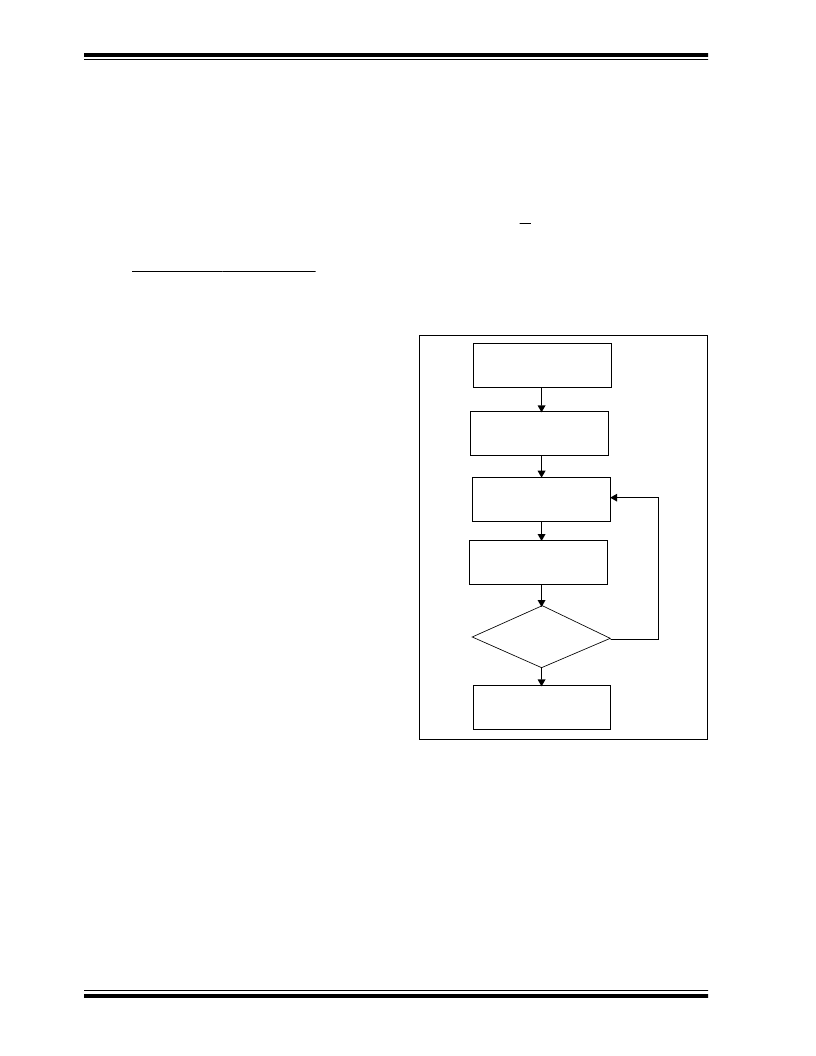

FIGURE 6-1:

ACKNOWLEDGE POLLING

FLOW

Send

Write Command

Send Stop

Condition to

Initiate Write Cycle

Send Start

Send Control Byte

with R/W = 0

Did Device

Acknowledge

(ACK = 0)

Next

Operation

NO

YES

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24C65-ISM | 64K 5.0V I 2 C Smart Serial EEPROM |

| 24C65-P | 64K 5.0V I 2 C Smart Serial EEPROM |

| 24C65-SM | 64K 5.0V I 2 C Smart Serial EEPROM |

| 24CMD25 | Analog IC |

| 24CME25 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24C65-ISM | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:64K 5.0V I 2 C Smart Serial EEPROM |

| 24C65-P | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:64K 5.0V I 2 C Smart Serial EEPROM |

| 24C65SM | 制造商:Microchip Technology Inc 功能描述: |

| 24C65-SM | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:64K 5.0V I 2 C Smart Serial EEPROM |

| 24C65T/P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。