- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371389 > 24LC00-EOT (Microchip Technology Inc.) 128 Bit I 2 C? Bus Serial EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | 24LC00-EOT |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | 128 Bit I 2 C? Bus Serial EEPROM |

| 中文描述: | 128位的I 2 C?總線串行EEPROM |

| 文件頁(yè)數(shù): | 8/18頁(yè) |

| 文件大?。?/td> | 264K |

| 代理商: | 24LC00-EOT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

24AA00/24LC00/24C00

DS21178D-page 8

2003 Microchip Technology Inc.

8.0

READ OPERATIONS

Read operations are initiated in the same way as write

operations with the exception that the R/W bit of the

slave address is set to one. There are three basic types

of read operations: current address read, random read,

and sequential read.

8.1

Current Address Read

The 24XX00 contains an address counter that main-

tains the address of the last word accessed, internally

incremented by one. Therefore, if the previous read

access was to address n, the next current address read

operation would access data from address n + 1. Upon

receipt of the slave address with the R/W bit set to one,

the device issues an acknowledge and transmits the

eight-bit data word. The master will not acknowledge

the transfer but does generate a Stop condition and the

device discontinues transmission (Figure 8-1).

8.2

Random Read

Random read operations allow the master to access

any memory location in a random manner. To perform

this type of read operation, first the word address must

be set. This is done by sending the word address to the

device as part of a write operation.

After the word address is sent, the master generates a

Start condition following the acknowledge. This termi-

nates the write operation, but not before the internal

address pointer is set. Then the master issues the

control byte again but with the R/W bit set to a one. The

24XX00 will then issue an acknowledge and transmits

the eight bit data word. The master will not acknowl-

edge the transfer but does generate a Stop condition

and the device discontinues transmission (Figure 8-2).

After this command, the internal address counter will

point to the address location following the one that was

just read.

8.3

Sequential Read

Sequential reads are initiated in the same way as a

random read except that after the device transmits the

first data byte, the master issues an acknowledge as

opposed to a Stop condition in a random read. This

directs the device to transmit the next sequentially

addressed 8-bit word (Figure 8-3).

To provide sequential reads the 24XX00 contains an

internal address pointer which is incremented by one at

the completion of each read operation. This address

pointer allows the entire memory contents to be serially

read during one operation.

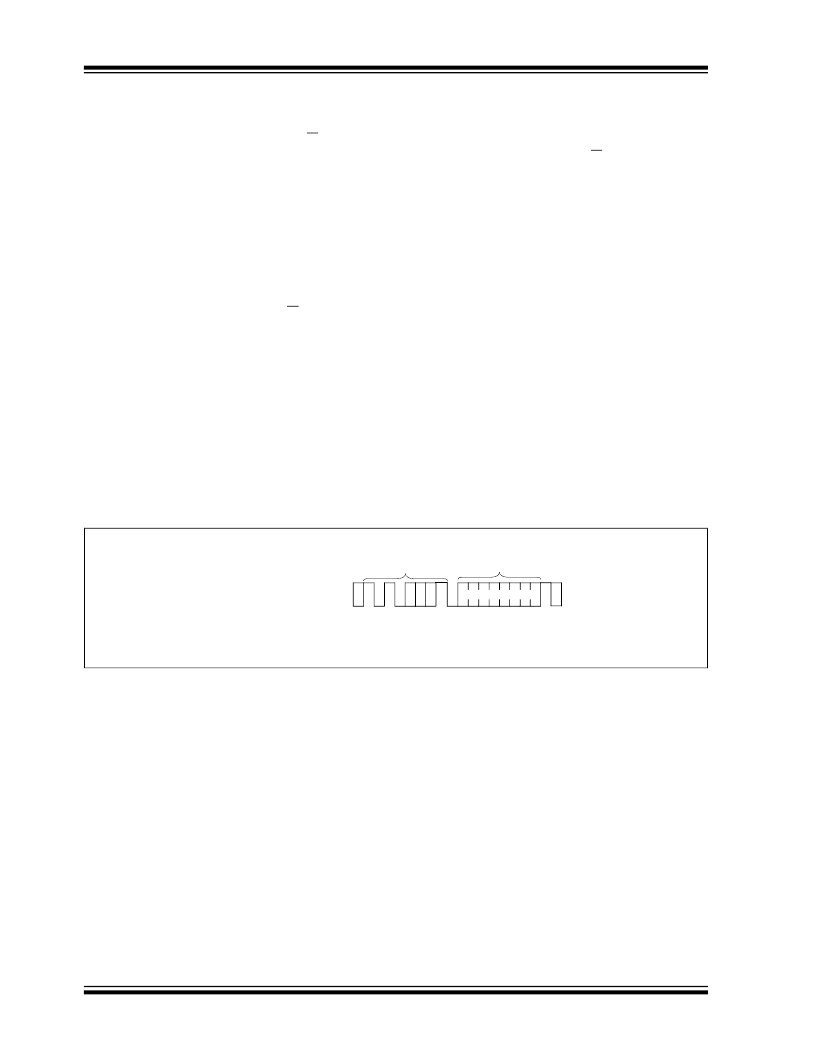

FIGURE 8-1:

CURRENT ADDRESS READ

BUS ACTIVITY

MASTER

SDA LINE

BUS ACTIVITY

P

S

S

T

O

P

CONTROL

BYTE

S

T

A

R

T

DATA

A

C

K

N

O

A

C

K

1

1

0

0 X X X 1

X = Don’t Care Bit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24LC00T-ST | 128 Bit I 2 C? Bus Serial EEPROM |

| 24AA00T-ESN | 128 Bit I 2 C? Bus Serial EEPROM |

| 24AA00-OT | 128 Bit I 2 C? Bus Serial EEPROM |

| 24AA00-EST | 128 Bit I 2 C? Bus Serial EEPROM |

| 24AA00-IOT | 128 Bit I 2 C? Bus Serial EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24LC00-EP | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:128 Bit I 2 C? Bus Serial EEPROM |

| 24LC00-ESN | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:128 Bit I2C Bus Serial EEPROM |

| 24LC00-EST | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:128 Bit I 2 C? Bus Serial EEPROM |

| 24LC00-I/MC | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:128 Bit I2C Bus Serial EEPROM |

| 24LC00-I/OT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:I2C Serial EEPROM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。