- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371400 > 24WC16 1K/2K/4K/8K/16K-Bit Serial E2PROM PDF資料下載

參數(shù)資料

| 型號: | 24WC16 |

| 英文描述: | 1K/2K/4K/8K/16K-Bit Serial E2PROM |

| 中文描述: | 1K/2K/4K/8K/16K-Bit串行E2PROM |

| 文件頁數(shù): | 5/9頁 |

| 文件大小: | 45K |

| 代理商: | 24WC16 |

CAT24WC01/02/04/08/16

5

Doc. No. 25051-00 3/98 S-1

using either 24WC01 or 24WC02 device. All three

address pins are used for these densities. If only one

24WC02 is addressed on the bus, all three address pins

(A0, A1and A2) can be left floating or connected to V

SS

.

If only one 24WC01 is addressed on the bus, all three

address pins (A0, A1and A2) must be connected to V

SS

.

A total of four devices can be addressed on a single bus

when using 24WC04 device. Only A1 and A2 address

pins are used with this device. The A0 address pin is a

no connect pin and can be tied to V

SS

or left floating. If

only one 24WC04 is being addressed on the bus, the

address pins (A1 and A2) can be left floating or con-

nected to V

SS

.

Only two devices can be cascaded when using 24WC08.

The only address pin used with this device is A2. The A0

and A1 address pins are no connect pins and can be tied

to V

SS

or left floating. If only one 24WC08 is being

addressed on the bus, the address pin (A2) can be left

floating or connected to V

SS

.

The 24WC16 is a stand alone device. In this case, all

address pins (A0, A1and A2) are no connect pins and

can be tied to V

SS

or left floating.

WP:

Write Protect

If the WP pin is tied to V

CC

the entire memory array

becomes Write Protected (READ only). When the WP

pin is tied to V

SS

or left floating normal read/write opera-

tions are allowed to the device.

I

2

C BUS PROTOCOL

The following defines the features of the I

2

C bus proto-

col:

(1) Data transfer may be initiated only when the bus is

not busy.

(2) During a data transfer, the data line must remain

stable whenever the clock line is high. Any changes

in the data line while the clock line is high will be

interpreted as a START or STOP condition.

START Condition

The START Condition precedes all commands to the

device, and is defined as a HIGH to LOW transition of

SDA when SCL is HIGH. The CAT24WC01/02/04/08/16

monitor the SDA and SCL lines and will not respond until

this condition is met.

STOP Condition

A LOW to HIGH transition of SDA when SCL is HIGH

determines the STOP condition. All operations must end

with a STOP condition.

DEVICE ADDRESSING

The bus Master begins a transmission by sending a

START condition. The Master then sends the address

of the particular slave device it is requesting. The four

most significant bits of the 8-bit slave address are fixed

as 1010 for the CAT24WC01/02/04/08/16 (see Fig. 5).

The next three significant bits (A2, A1, A0) are the device

address bits and define which device or which part of the

device the Master is accessing. Up to eight CAT24WC01/

02, four CAT24WC04, two CAT24WC08, and one

CAT24WC16 may be individually addressed by the

system. The last bit of the slave address specifies

whether a Read or Write operation is to be performed.

When this bit is set to 1, a Read operation is selected,

and when set to 0, a Write operation is selected.

After the Master sends a START condition and the slave

address byte, the CAT24WC01/02/04/08/16 monitors

the bus and responds with an acknowledge (on the SDA

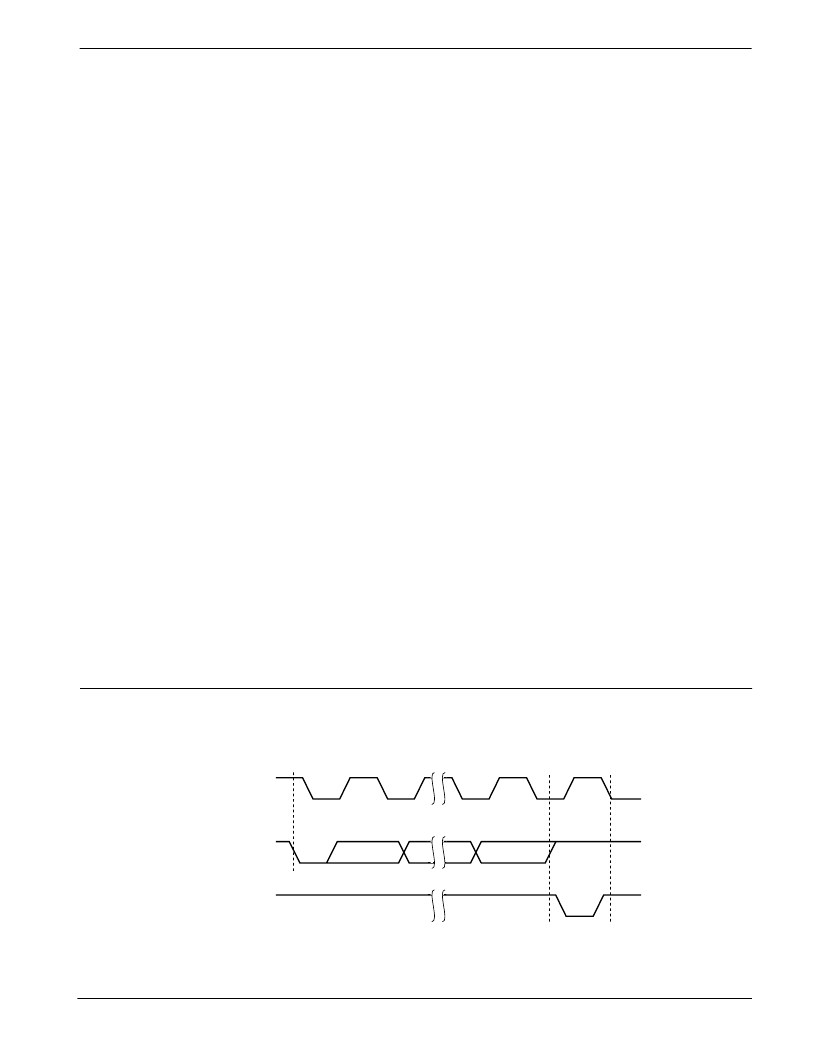

Figure 4. Acknowledge Timing

5020 FHD F06

ACKNOWLEDGE

1

START

SCL FROM

MASTER

8

9

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24WC128 | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| 24WC32 | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| 250-8501-010 | Low-Power, SPST, Fast, CMOS Analog Switch |

| 2500-10J | Molded Unshielded RF Coils |

| 2500-00J | Molded Unshielded RF Coils |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24WC256KI | 制造商:CSI 功能描述: |

| 24WC32 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:32K/64K-Bit I2C Serial CMOS E2PROM |

| 24WC32P | 制造商:CATALYST 功能描述: |

| 24WR10KLFTR | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:4mm Diameter Single Turn Cermet Trimming Potentiometer |

| 24X | 功能描述:燈 24V .035A RoHS:否 制造商:Chicago Miniature 燈類型:Incandescent 燈座類型:Wire Terminal 燈大小:T-1 3/4 顏色: 電壓:14 V 工作電流: MSCP:0.3 MSCP 壽命:40000 hr 封裝:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。