- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371422 > 27C17A-15IVS (Microchip Technology Inc.) GIGABASE 350 CAT5E PATCH 4 FT, NON BOOT, BLUE PDF資料下載

參數(shù)資料

| 型號: | 27C17A-15IVS |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | GIGABASE 350 CAT5E PATCH 4 FT, NON BOOT, BLUE |

| 中文描述: | 16K的(2K × 8)的CMOS EEPROM的 |

| 文件頁數(shù): | 1/8頁 |

| 文件大?。?/td> | 67K |

| 代理商: | 27C17A-15IVS |

1996 Microchip Technology Inc.

DS11127G-page 1

FEATURES

Fast Read Access Time—150 ns

CMOS Technology for Low Power Dissipation

- 30 mA Active

- 100

μ

A Standby

Fast Byte Write Time—200

Data Retention >200 years

High Endurance - Minimum 10

Automatic Write Operation

- Internal Control Timer

- Auto-Clear Before Write Operation

- On-Chip Address and Data Latches

Data Polling; Ready/Busy

Chip Clear Operation

Enhanced Data Protection

- V

CC

Detector

- Pulse Filter

- Write Inhibit

Electronic Signature for Device Identification

5-Volt-Only Operation

Organized 2Kx8 JEDEC Standard Pinout

- 28 Pin Dual-In-Line Package

- 32-Pin PLCC Package

- 28-Pin Thin Small Outline Package (TSOP)

8x20mm

- 28-Pin Very Small Outline Package (VSOP)

8x13.4mm

Available for Extended Temperature Ranges:

- Commercial: 0C to +70C

- Industrial: -40C to +85C

μ

s or 1 ms

4

Erase/Write Cycles

DESCRIPTION

volatile electrically Erasable PROM. The 28C17A is

accessed like a static RAM for the read or write cycles without

the need of external components. During a “byte write”, the

address and data are latched internally, freeing the micropro-

cessor address and data bus for other operations. Following

the initiation of write cycle, the device will go to a busy state

and automatically clear and write the latched data using an

internal control timer. To determine when the write cycle is

complete, the user has a choice of monitoring the Ready/

Busy output or using Data polling. The Ready/Busy pin is an

open drain output, which allows easy configuration in wired-

or systems. Alternatively, Data polling allows the user to read

the location last written to when the write operation is com-

plete. CMOS design and processing enables this part to be

used in systems where reduced power consumption and reli-

ability are required. A complete family of packages is offered

to provide the utmost flexibility in applications.

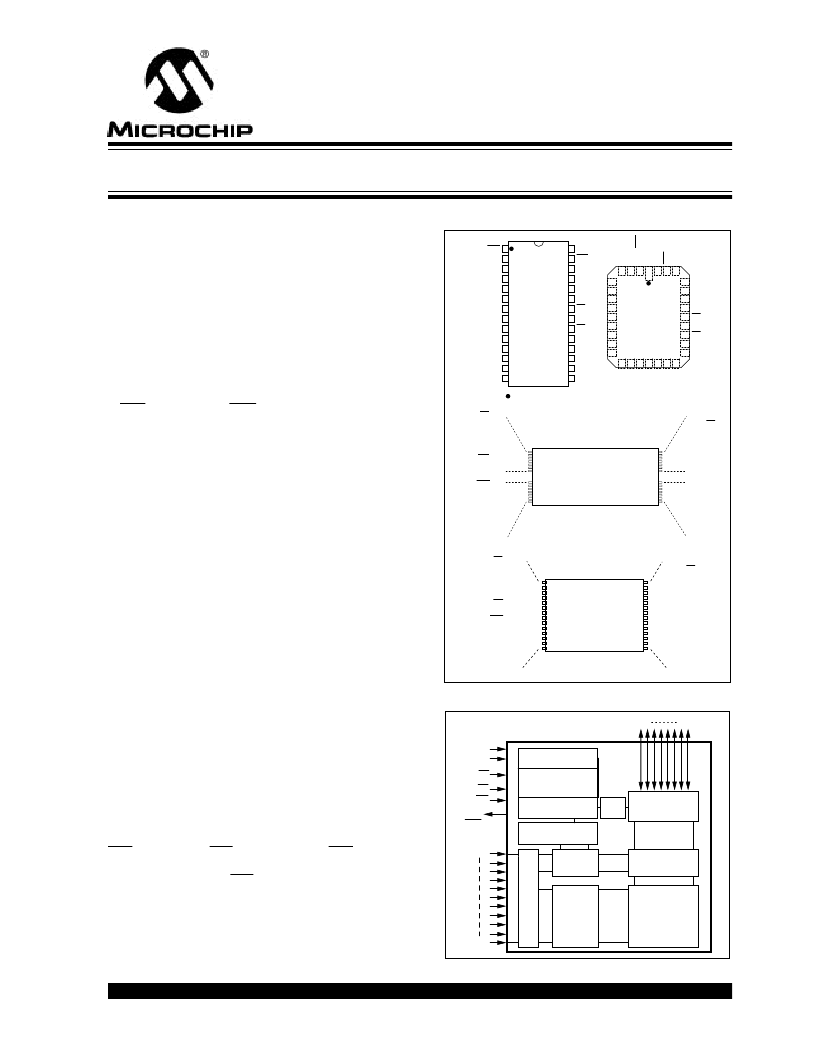

PACKAGE TYPES

BLOCK DIAGRAM

Pin 1 indicator on PLCC on top of package

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RDY/BSY

NC

A7

A6

A5

A4

A3

A2

A1

A0

I/O0

I/O1

I/O2

V

SS

Vcc

WE

NC

A8

A9

NC

OE

A10

CE

I/O7

I/O6

I/O5

I/O4

I/O3

A6

A5

A4

A3

A2

A1

A0

NC

I/O0

A8

A9

NC

NC

OE

A10

CE

I/O7

I/O6

A

4

N

3

R

2

N

1

V

3

W

3

N

3

I

I

V

N

I

I

I

1

1

1

1

1

1

2

29

28

27

26

25

24

23

22

21

5

6

7

8

9

10

11

12

13

OE

NC

A9

A8

NC

WE

Vcc

RDY/BSY

NC

A7

A6

A5

A4

A3

A10

CE

I/07

I/06

I/05

I/04

I/03

Vss

I/02

I/01

I/00

A0

A1

A2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

A10

CE

I/O7

I/O6

I/O5

I/O4

I/O3

21

20

19

18

17

16

15

V

SS

I/O2

I/O1

I/O0

A0

A1

A2

14

13

12

11

10

9

8

OE

NC

A9

A8

NC

WE

CC

22

23

24

25

26

27

28

RDY/V

NC

A7

A6

A5

A4

A3

1

2

3

4

5

6

7

D

P

T

V

I/O0

I/O7

InBuffers

Chip Enable/

Output Enable

Control Logic

Auto Erase/Write

Timing

CE

OE

WE

Data Protection

Circuitry

A10

Y Gating

16K bit

Cell Matrix

X

Decoder

Y

Decoder

A0

Data

Poll

V

CC

V

SS

L

a

t

c

h

e

s

Program Voltage

Generation

Rdy/

Busy

28C17A

16K (2K x 8) CMOS EEPROM

This document was created with FrameMaker 4 0 4

相關PDF資料 |

PDF描述 |

|---|---|

| 27C17A-15L | CAT 5E PATCH CORD, BLUE, 6 FT |

| 27C17AF-15IVS | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 27C17AT-15IVS | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 27C17A-25IVS | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 27C17AF-25IVS | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 27C17A-15L | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:16K (2K x 8) CMOS EEPROM |

| 27C17A-15P | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:16K (2K x 8) CMOS EEPROM |

| 27C17A-15TS | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:16K (2K x 8) CMOS EEPROM |

| 27C17A-15VS | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:16K (2K x 8) CMOS EEPROM |

| 27C17A-20IL | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:16K (2K x 8) CMOS EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。