- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371430 > 27LV64-20IP (Microchip Technology Inc.) 64K (8K x 8) Low-Voltage CMOS EPROM PDF資料下載

參數(shù)資料

| 型號(hào): | 27LV64-20IP |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | 64K (8K x 8) Low-Voltage CMOS EPROM |

| 中文描述: | 64K的(8K的× 8)低電壓的CMOS存儲(chǔ)器 |

| 文件頁數(shù): | 6/12頁 |

| 文件大?。?/td> | 62K |

| 代理商: | 27LV64-20IP |

27LV64

DS11024E-page 6

1996 Microchip Technology Inc.

1.3

Standby Mode

The standby mode is defined when the CE pin is high

(V

IH

) and a program mode is not defined.

When these conditions are met, the supply current will

drop from 20 mA to 100

μ

A.

1.4

Output Enable

This feature eliminates bus contention in microproces-

sor-based systems in which multiple devices may drive

the bus. The outputs go into a high impedance state

when the following condition is true:

The OE and PGM pins are both high.

1.5

Erase Mode (U.V. Windowed Versions)

Windowed products offer the capability to erase the

memory array. The memory matrix is erased to the all

1’s state when exposed to ultraviolet light. To ensure

complete erasure, a dose of 15 watt-second/cm

2

is

required. This means that the device window must be

placed within one inch and directly underneath an ultra-

violet lamp with a wavelength of 2537 Angstroms,

intensity of 12,000

μ

W/cm

2

for approximately 20 min-

utes.

1.6

Programming Mode

The Express Algorithm has been developed to improve

the programming throughput times in a production

environment. Up to ten 100-microsecond pulses are

applied until the byte is verified. No overprogramming

is required. A flowchart of the express algorithm is

shown in Figure 1-3.

Programming takes place when:

a)

V

CC

is brought to the proper voltage,

b)

V

PP

is brought to the proper V

H

level,

c)

the CE pin is low,

d)

the OE pin is high, and

e)

the PGM pin is low.

Since the erased state is “1” in the array, programming

of “0” is required. The address to be programmed is set

via pins A0-A12 and the data to be programmed is pre-

sented to pins O0-O7. When data and address are sta-

ble, OE is high, CE is low and a low-going pulse on the

PGM line programs that location.

1.7

Verify

After the array has been programmed it must be veri-

fied to ensure all the bits have been correctly pro-

grammed. This mode is entered when all the following

conditions are met:

a)

V

CC

is at the proper level,

b)

V

PP

is at the proper V

H

level,

c)

the CE line is low,

d)

the PGM line is high, and

e)

the OE line is low.

1.8

Inhibit

When programming multiple devices in parallel with dif-

ferent data, only CE or PGM need be under separate

control to each device. By pulsing the CE or PGM line

low on a particular device in conjunction with the PGM

or CE line low, that device will be programmed; all other

devices with CE or PGM held high will not be pro-

grammed with the data, although address and data will

be available on their input pins (i.e., when a high level

is present on CE or PGM); and the device is inhibited

from programming.

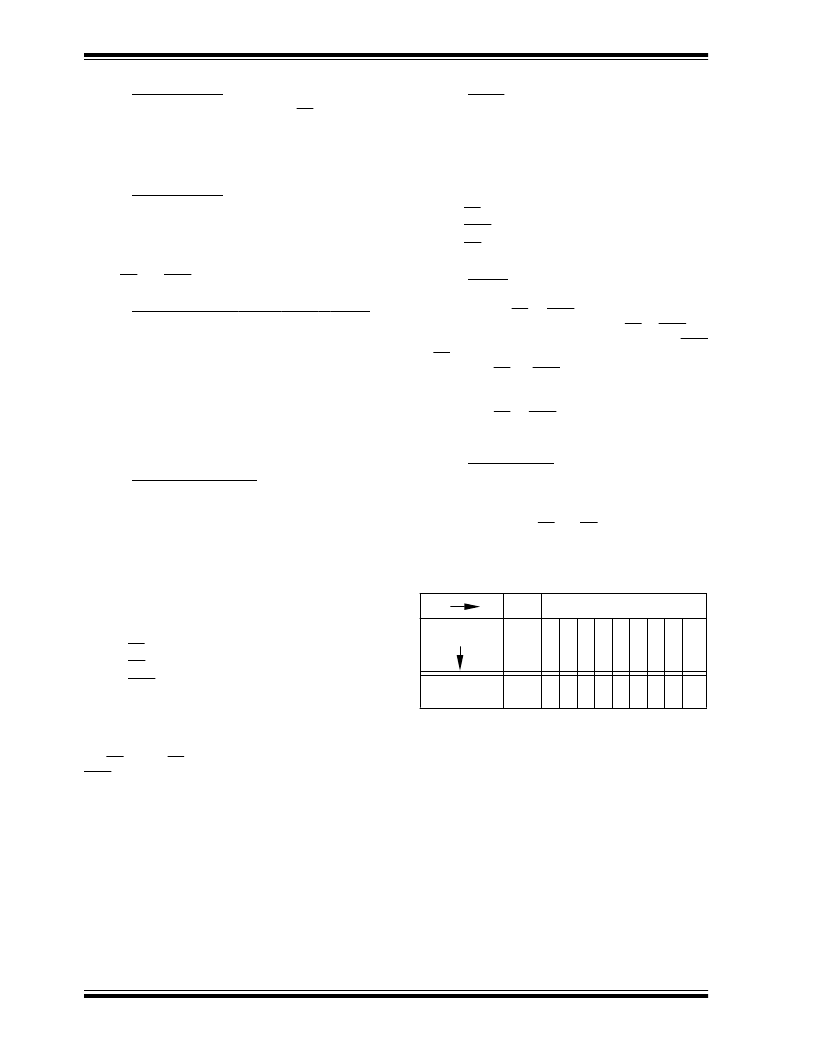

1.9

Identity Mode

In this mode specific data is output which identifies the

manufacturer as Microchip Technology Inc. and device

type. This mode is entered when Pin A9 is taken to V

H

(11.5V to 12.5V). The CE and OE lines must be at V

IL

.

A0 is used to access any of the two non-erasable bytes

whose data appears on O0 through O7.

Pin

Input

Output

Identity

A0

0

7

O

6

O

5

O

4

O

3

O

2

O

1

O

0

H

e

x

Device Type*

V

IL

V

IH

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

0

29

02

* Code subject to change

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 27LV64-20ISO | 64K (8K x 8) Low-Voltage CMOS EPROM |

| 27LV64-20L | 64K (8K x 8) Low-Voltage CMOS EPROM |

| 27LV64-20P | 64K (8K x 8) Low-Voltage CMOS EPROM |

| 27LV64-20SO | 64K (8K x 8) Low-Voltage CMOS EPROM |

| 27LV64-25IP | 64K (8K x 8) Low-Voltage CMOS EPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 27LV64-20ISO | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:64K (8K x 8) Low-Voltage CMOS EPROM |

| 27LV64-20L | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:64K (8K x 8) Low-Voltage CMOS EPROM |

| 27LV64-20P | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:64K (8K x 8) Low-Voltage CMOS EPROM |

| 27LV64-20SO | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:64K (8K x 8) Low-Voltage CMOS EPROM |

| 27LV64-25/J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 EPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。