- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371434 > 28F002BC (Intel Corp.) 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY PDF資料下載

參數(shù)資料

| 型號: | 28F002BC |

| 廠商: | Intel Corp. |

| 英文描述: | 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| 中文描述: | 28F002BC的2 - Mbit(256K × 8)引導(dǎo)塊閃存 |

| 文件頁數(shù): | 13/37頁 |

| 文件大小: | 455K |

| 代理商: | 28F002BC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

E

with altering memory contents are accessible via

the CUI.

28F002BC 2-MBIT BOOT BLOCK FLASH MEMORY

13

PRELIMINARY

The purpose of the Write State Machine (WSM) is

to automate the write and erasure of the device

completely. The WSM will begin operation upon

receipt of a signal from the CUI and will report

status back through the status register. The CUI will

handle the WE# interface to the data and address

latches, as well as system software requests for

status while the WSM is in operation.

3.1

Bus Operations

Flash memory reads, erases and writes in-system

via the local CPU. All bus cycles to or from the flash

memory conform to standard microprocessor bus

cycles. These bus operations are summarized in

Tables 2 and 4.

3.2

Read Operations

The 28F002BC has three user read modes: read

array, read intelligent identifier, and read status

register.

During power-up conditions, it takes a maximum of

600 ns from when V

CC

is at 4.5V to when valid data

is available at the outputs.

3.2.1

READ ARRAY

When RP# transitions from V

IL

(reset) to V

IH

, the

device will be in read array mode and will respond

to the read control inputs (CE#, OE#, and address

inputs) without any commands being written to the

CUI.

When the device is in read array mode, four control

signals must be manipulated to read data at the

outputs.

WE# must be logic high (V

IH

)

CE# must be logic low (V

IL

)

OE# must be logic low (V

IL

)

RP# must be logic high (V

IH

)

In addition, the address of the desired location must

be applied to the address pins. Refer to AC

Characteristics for the exact sequence and timing

of these signals.

If the device is not in read array mode, as would be

the case after a program or erase operation, the

Read Mode command (FFH) must be written to the

CUI before array reads can take place.

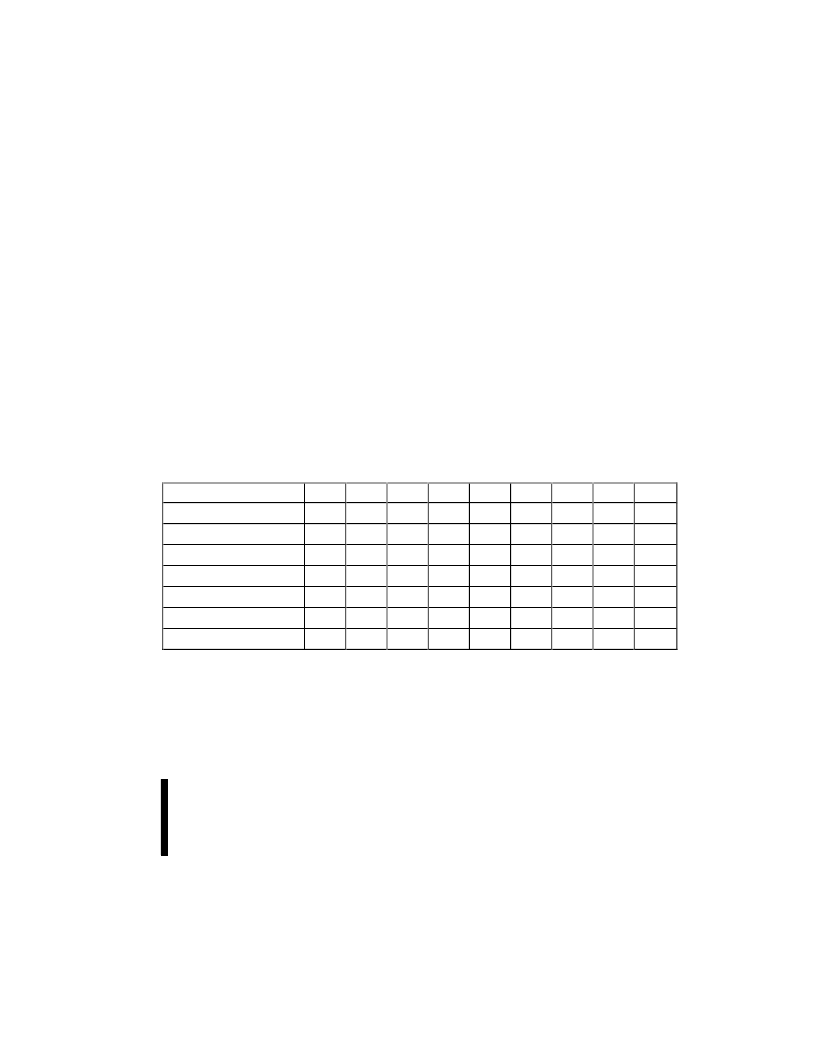

Table 2. 28F002BC Bus Operations

Mode

Notes

RP#

CE#

OE#

WE#

A

9

A

0

V

PP

DQ

0

–7

Read

1,2,3

V

IH

V

IL

V

IL

V

IH

X

X

X

D

OUT

Output Disable

V

IH

V

IL

V

IH

V

IH

X

X

X

High Z

Standby

V

IH

V

IH

X

X

X

X

X

High Z

Deep Power-Down

8

V

IL

X

X

X

X

X

X

High Z

Intelligent Identifier (Mfr)

4

V

IH

V

IL

V

IL

V

IH

V

ID

V

IL

X

89H

Intelligent Identifier (Device)

4

V

IH

V

IL

V

IL

V

IH

V

ID

V

IH

X

7CH

Write

5,6,7

V

IH

V

IL

V

IH

V

IL

X

X

V

PPH

D

IN

NOTES:

1. Refer to DC Characteristics.

2. X can be V

IL

, V

IH

for control pins and addresses, V

PPLK

or V

PPH

for V

PP

.

3. See DC Characteristics for V

PPLK

, V

PPH

, V

HH

, V

ID

voltages.

4. Manufacturer and device codes may also be accessed via a CUI write sequence, A

1

-A

17

= X.

5. Refer to Table 3 for valid D

IN

during a write operation.

6. Command writes for program or block erase are only executed when V

PP

= V

PPH

.

7. To write or erase the boot block, hold RP# at V

HH

.

8. RP# must be at GND

±

0.2V to meet the maximum deep power-down current specified.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F002BV-B | 2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 28F004B3 | 3 Volt Advanced Boot Block Flash Memory(3 V,4M位高級引導(dǎo)塊閃速存儲器) |

| 28F004S3 | BYTE-WIDE SMART 3 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| 28F004S5 | BYTE-WIDE SMART 5 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| 28F004SC | BYTE-WIDE SmartVoltage FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F002BL-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT (128K x 16. 256K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F002BL-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT (128K x 16. 256K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F002BV-B | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 28F002BV-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 28F002BV-T/B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SmartVoltage Boot Block Flash Memory Fa |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。