- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368967 > 29K_RESET 5-Pin, Multiple-Input, Programmable Reset ICs PDF資料下載

參數(shù)資料

| 型號: | 29K_RESET |

| 英文描述: | 5-Pin, Multiple-Input, Programmable Reset ICs |

| 中文描述: | 同步復位和BOOTW *避免配置不當ROM的銀行0寬度 |

| 文件頁數(shù): | 1/3頁 |

| 文件大?。?/td> | 89K |

| 代理商: | 29K_RESET |

AMD

29K

Family

Technical

Bulletin

Synchronizing

RESET

Misconfiguring ROM Bank 0 Width

and

BOOTW

to Avoid

EPD Systems Engineering

November 15, 1993

Purpose

This bulletin replaces the technical bulletin entitled

RESET-BOOTW Synchronization

, PID No. 18011,

and its first revision,

RESET-BOOTW Correction

,

PID No. 18011A. This revision includes the

Revision B Am29200 microcontroller as an affected

part, and incorporates minor, nontechnical changes

throughout.

The only nonreserved selection where

BOOTW

has a

different value before and after a reset is an 8-bit-

wide boot bank. For this option,

RESET

are tied together. Any nonzero skew between these

two signals can result in the possibility of

misconfiguring the boot bank.

––––– and

BOOTW

on

approximately the rising edge of

MEMCLK

. It is

difficult to be specific because during a processor

reset, the clocks may not be established yet. In

particular,

MEMCLK

is not guaranteed externally until

after

RESET

––––– and

BOOTW

The processor samples

RESET

––––– is deasserted.

The 29K Family microcontrollers support 8-, 16-,

and 32-bit-wide ROM banks. Configuring an 8-bit-

wide boot bank (ROM Bank 0) requires that

BOOTW

and

RESET

between these two signals can result in the

possibility of misconfiguring the width of ROM

Bank 0. This technical bulletin describes the cause

and probability of such a misconfiguration and

discusses possible solutions, including an example

circuit.

––––– be tied together. Any nonzero skew

When the processor recognizes the deassertion of

RESET

––––– (the first sample where

RESET

compares the new and previous samples of

BOOTW

.

If a rising

MEMCLK

edge occurs during the skew

region of the

RESET

misconfiguration may occur.

––––– is High), it

BOOTW

signals, a

Affected Parts

The information in this bulletin affects the following

parts:

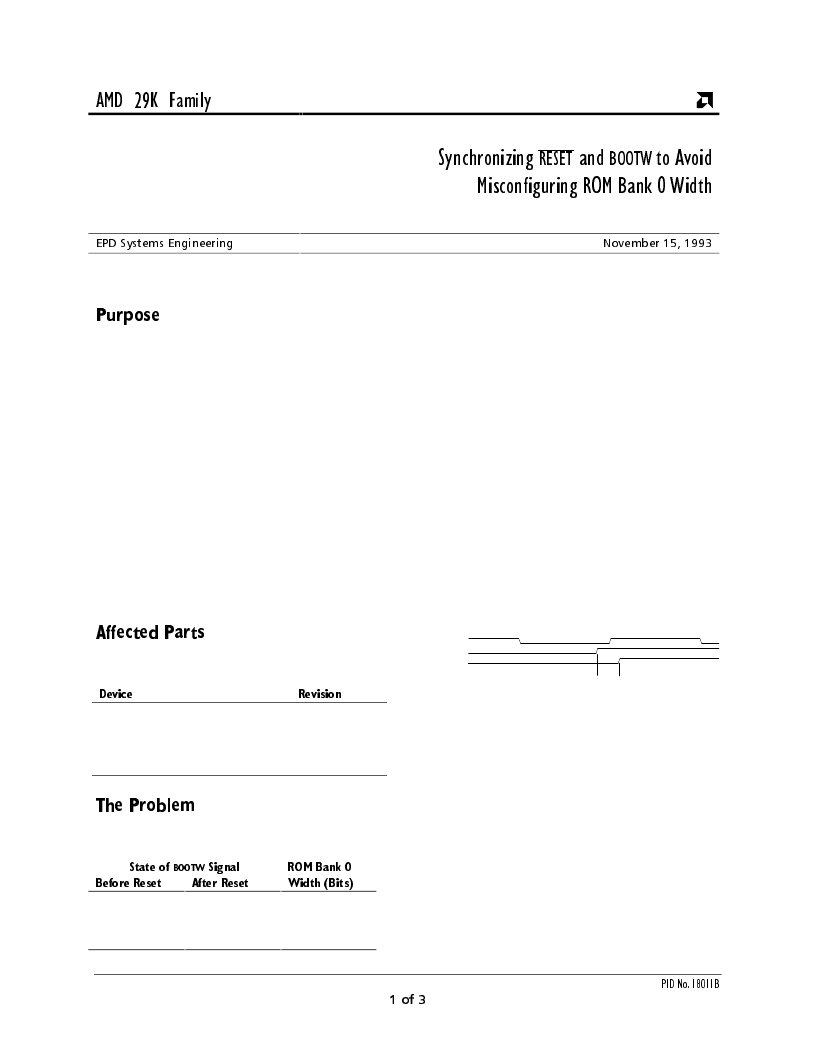

MEMCLK

*RESET

BOOTW

skew

Device

Am29200

microcontroller

Am29205

microcontroller

Am29240

microcontroller

Am29243

microcontroller

Am29245

microcontroller

Revision

A, B

A

A

A

A

Again, it is difficult to know whether a

misconfiguration will actually occur because of

uncertainties in the signal-hardening logic and phase

relationships of internal processor clocks. A

misconfiguration is externally visible by an

instruction fetch stream indicative of 16- or 32-bit-

wide memory (0, 2, 4, ..., or 0, 4, 8, ...) instead of the

intended 8-bit-wide bank (0, 1, 2, ...).

The Problem

The state of

BOOTW

before and after the deassertion

of

RESET

––––– determines the width of ROM Bank 0.

In a production environment, it is impossible to

guarantee zero skew between the

BOOTW

and

pins of the processor, or account for varying

processor internal delays due to process variations.

–––––

State of

BOOTW

Signal

Before Reset

0

1

0

1

ROM Bank 0

Width (Bits)

16

32

After Reset

0

1

1

0

Assuming a random distribution of

deassertions relative to

INCLK

, the probability of

–––––

8

(reserved)

PID No. 18011B

1 of 3

相關PDF資料 |

PDF描述 |

|---|---|

| 29K_SUPMODE | Am29030 and Am29035 Microprocessors Defining a Trap to Switch to Supervisor Mode |

| 29KPROG | 5-Pin, Multiple-Input, Programmable Reset ICs |

| 29W040 | 4 Mbit 512Kb x8, Uniform Block Low Voltage Single Supply Flash Memory |

| 2A-50C | RADIATION HARDENED HIGH EFFICIENCY, 5 AMP SWITCHING REGULATORS |

| 2A01-T | 2.0A RECTIFIER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 29L06 | 制造商:CLARKSON 功能描述:CSN HSS SCRW/SHK RNDG CUTTER 3MM |

| 29L10 | 制造商:CLARKSON 功能描述:CSN HSS SCRW/SHK RNDG CUTTER 5MM |

| 29L102C | 功能描述:固定電感器 1.0uH 4.6A Shielded SMD RoHS:否 制造商:AVX 電感:10 uH 容差:20 % 最大直流電流:1 A 最大直流電阻:0.075 Ohms 工作溫度范圍:- 40 C to + 85 C 自諧振頻率:38 MHz Q 最小值:40 尺寸:4.45 mm W x 6.6 mm L x 2.92 mm H 屏蔽:Shielded 端接類型:SMD/SMT 封裝 / 箱體:6.6 mm x 4.45 mm |

| 29L103C | 功能描述:固定電感器 10uH 1.55A Shielded SMD RoHS:否 制造商:AVX 電感:10 uH 容差:20 % 最大直流電流:1 A 最大直流電阻:0.075 Ohms 工作溫度范圍:- 40 C to + 85 C 自諧振頻率:38 MHz Q 最小值:40 尺寸:4.45 mm W x 6.6 mm L x 2.92 mm H 屏蔽:Shielded 端接類型:SMD/SMT 封裝 / 箱體:6.6 mm x 4.45 mm |

| 29L104C | 功能描述:固定電感器 100uH 480mA Shielded SMD RoHS:否 制造商:AVX 電感:10 uH 容差:20 % 最大直流電流:1 A 最大直流電阻:0.075 Ohms 工作溫度范圍:- 40 C to + 85 C 自諧振頻率:38 MHz Q 最小值:40 尺寸:4.45 mm W x 6.6 mm L x 2.92 mm H 屏蔽:Shielded 端接類型:SMD/SMT 封裝 / 箱體:6.6 mm x 4.45 mm |

發(fā)布緊急采購,3分鐘左右您將得到回復。