- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298320 > 3D7424-1 (DATA DELAY DEVICES INC) MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE PDF資料下載

參數(shù)資料

| 型號: | 3D7424-1 |

| 廠商: | DATA DELAY DEVICES INC |

| 元件分類: | 延遲線 |

| 英文描述: | MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 中文描述: | ACTIVE DELAY LINE, TRUE OUTPUT, PDIP14 |

| 封裝: | ROHS COMPLIANT, DIP-14 |

| 文件頁數(shù): | 3/6頁 |

| 文件大?。?/td> | 391K |

| 代理商: | 3D7424-1 |

3D7424

APPLICATION NOTES (CONT’D)

DELAY ACCURACY

There are a number of ways of characterizing the

delay accuracy of a programmable line. The first

is the differential nonlinearity (DNL), also referred

to as the increment error. It is defined as the

deviation of the delay step at a given address

from its nominal value. For all dash numbers, the

DNL is within 1/4 LSB at every address (see

Table 1: Delay Step).

The integrated nonlinearity (INL) is determined

by first constructing the least-squares best fit

straight line through the delay-versus-address

data. The INL is then the deviation of a given

delay from this line. For all dash numbers, the

INL is within 1.0 LSB at every address.

The relative error is defined as follows:

erel = (Ti – T0) – i * Tinc

where i is the address, Ti is the measured delay

at the i’th address, T0 is the measured inherent

delay, and Tinc is the nominal increment. It is very

similar to the INL, but simpler to calculate. For

most dash numbers, the relative error is less than

1/8 LSB at every address (see Table 1: Relative

Tolerance).

The absolute error is defined as follows:

eabs = Ti – (Tinh + i * Tinc)

where Tinh is the nominal inherent delay. The

absolute error tolerance is given for addresses 0

and 15 (see Table 1: Inherent Delay, Total Delay,

respectively). At any intermediate address, the

tolerance can be found via linear interpolation of

the address 0 & address 15 tolerances.

The matching error is a measure of how well the

delay of the four lines track each other when they

are all programmed to the same address. The

lines are typically matched to within 1% or 1ns,

whichever is greater, for all addresses and all

dash numbers.

DELAY STABILITY

The delay of CMOS integrated circuits is strongly

dependent on power supply and temperature.

The 3D7424 utilizes novel compensation circuitry

to minimize the delay variations induced by

fluctuations in power supply and/or temperature.

With regard to stability, the delay of the 3D7424

at a given address, i, can be split into two

components: the inherent delay (T0) and the

relative delay (Ti – T0). These components exhibit

very different stability coefficients, both of which

must be considered in very critical applications.

The thermal coefficient of the relative delay is

limited to

±250 PPM/C, which is equivalent to a

variation, over the -40C to 85C operating range,

of

±1.5% from the room-temperature delay

settings. This holds for dash numbers greater

than 1. For smaller dash numbers, the thermal

drift will be larger and will always be positive. The

thermal coefficient of the inherent delay is

nominally +15ps/C for all dash numbers.

The power supply sensitivity of the relative delay

is

±0.5% over the 4.75V to 5.25V operating

range, with respect to the delay settings at the

nominal 5.0V power supply. This holds for all

dash numbers greater than 1. For smaller dash

numbers, the voltage sensitivity will be greater

and will always be negative. The sensitivity of the

inherent delay is nominally -1ps/mV for all dash

numbers.

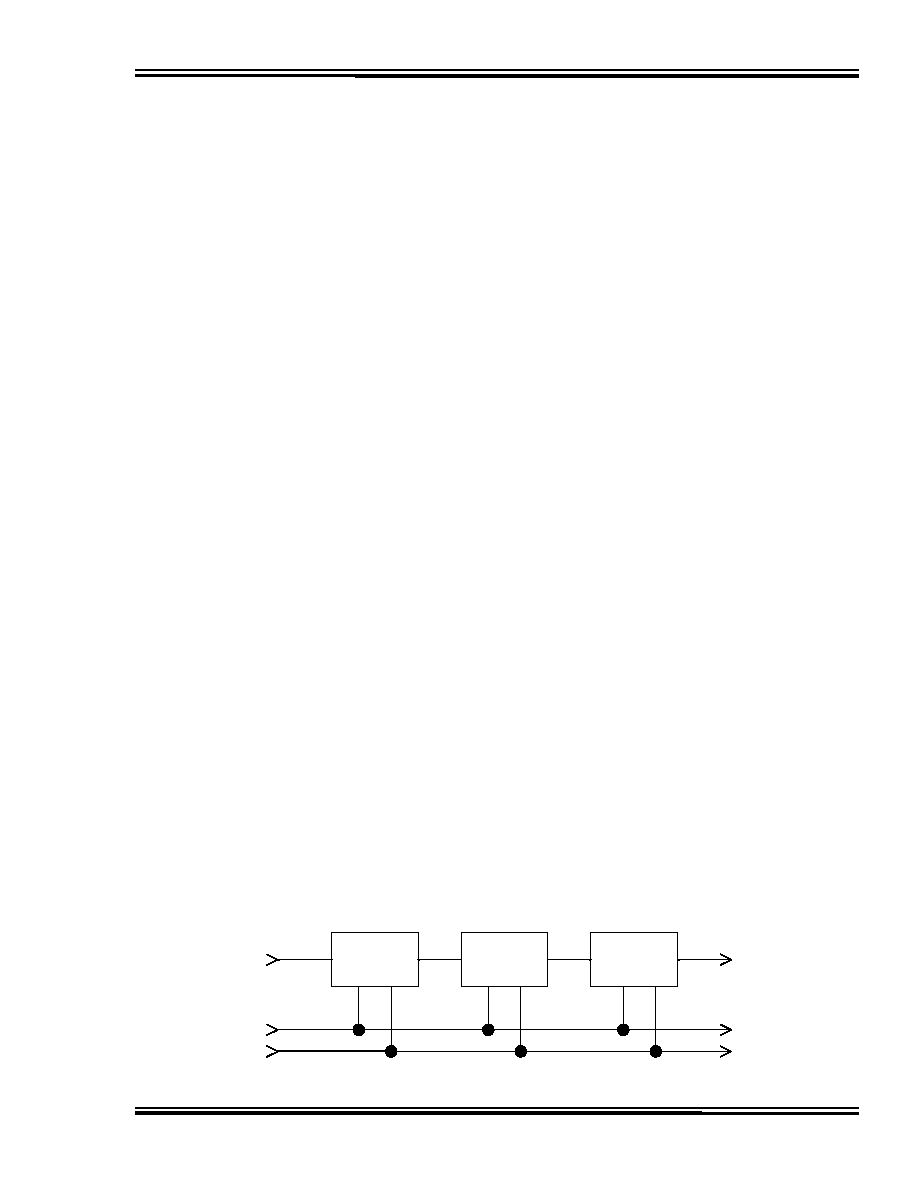

FROM

WRITING

DEVICE

TO

NEXT

DEVICE

SI

SO

SC

AL

3D7424

Figure 3: Cascading Multiple Devices

SI

SO

SC

AL

SI

SO

SC

AL

Doc #06019

DATA DELAY DEVICES, INC.

3

6/5/2006

3 Mt. Prospect Ave. Clifton, NJ 07013

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 3D7424-1.5 | MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 3D7424-10 | MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 3D7424-100 | MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 3D7424-15 | MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 3D7424-2 | MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 3D7424-1.5 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 3D7424-10 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 3D7424-100 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 3D7424-15 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

| 3D7424-2 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC QUAD 4-BIT PROGRAMMABLE DELAY LINE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。