- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄222475 > 5429FCT52CTSO (Integrated Device Technology, Inc.) LM140L/LM340L Series 3-Terminal Positive Regulators; Package: TO-39; No of Pins: 3; Qty per Container: 20; Container: Tray PDF資料下載

參數(shù)資料

| 型號: | 5429FCT52CTSO |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | LM140L/LM340L Series 3-Terminal Positive Regulators; Package: TO-39; No of Pins: 3; Qty per Container: 20; Container: Tray |

| 中文描述: | 快速CMOS八進制注冊收發(fā)器 |

| 文件頁數(shù): | 2/8頁 |

| 文件大小: | 125K |

| 代理商: | 5429FCT52CTSO |

IDT29FCT52AT/BT/CT/DT, IDT29FCT/2052AT/BT/CT, IDT29FCT53AT/BT/CT

FAST CMOS OCTAL REGISTERED TRANSCEIVERS

MILITARY AND COMMERCIAL TEMPERATURE RANGES

6.1

2

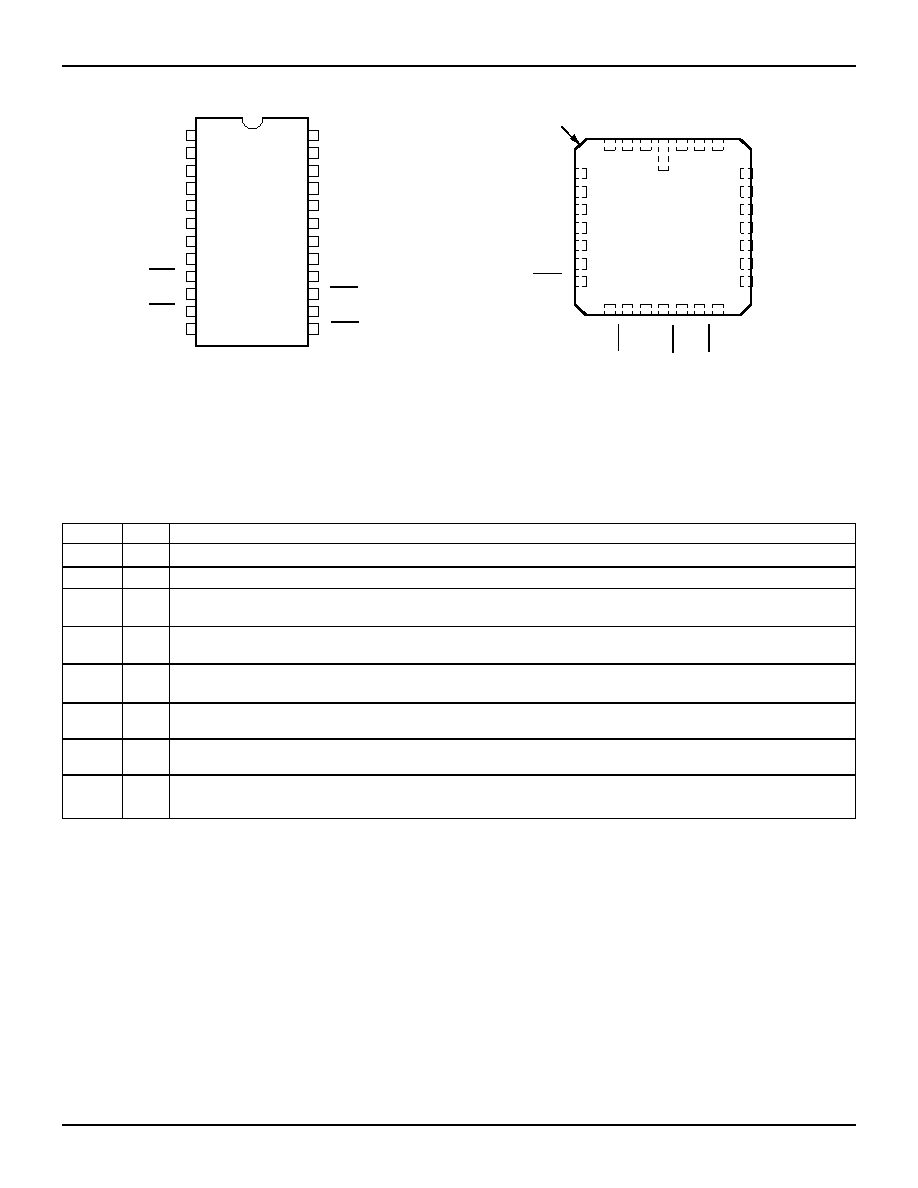

PIN CONFIGURATIONS

5

6

7

8

9

10

11

12

GND

1

2

3

4

24

23

22

21

20

19

18

17

Vcc

16

15

14

13

P24-1

D24-1

SO24-2

SO24-7*

SO24-8*

&

E24-1

A 6

A 5

A 4

A 3

A 2

CEB

CEA

CPB

CPA

OEA

A 1

A 0

A 7

B 6

B 5

B 4

B 3

B 2

B 1

B

B 7

0

OEB

2629 drw 02

5

6

7

8

9

10

11

L28-1

25

24

23

22

21

20

19

12 13 14 15 16 17 18

43

2

1

28 27 26

INDEX

2629 drw 03

B 3

B 2

B 1

B 0

A 5

A 4

A 3

A 2

A 1

A 0

OEB

NC

GND

CEB

CEA

CPB

CPA

OEA

NC

B 4

B

5

Vcc

A

6

A

7

B

6

NC

B

7

DIP/SOIC/SSOP/QSOP/CERPACK

TOP VIEW

LCC

TOP VIEW

* For 29FCT52/29FCT2052AT/BT/CT only

PIN DESCRIPTION

Name

I/O

Description

A0-7

I/O

Eight bidirectional lines carrying the A Register inputs or B Register outputs.

B0-7

I/O

Eight bidirectional lines carrying the B Register inputs or A Register outputs.

CPA

I

Clock for the A Register. When

CEA is LOW, data is entered into the A Register on the LOW-to-HIGH transition of

the CPA signal.

CEA

I

Clock Enable for the A Register. When

CEA is LOW, data is entered into the A Register on the LOW-to-HIGH transition

of the CPA signal. When

CEA is HIGH, the A Register holds its contents, regardless of CPA signal transitions.

OEB

I

Output Enable for the A Register. When

OEB is LOW, the A Register outputs are enabled onto the B0-7 lines. When

OEB is HIGH, the B0-7 outputs are in the high-impedance state.

CPB

I

Clock for the B Register. When

CEB is LOW, data is entered into the B Register on the LOW-to-HIGH transition of

the CPB signal.

CEB

I

Clock Enable for the B Register. When

CEB is LOW, data is entered into the B Register on the LOW-to-HIGH transition

of the CPB signal. When

CEB is HIGH, the B Register holds its contents, regardless of CPB signal transitions.

OEA

I

Output Enable for the B Register. When

OEA is LOW, the B Register outputs are enabled onto the A0-7 lines. When

OEA is HIGH, the A0-7 outputs are in the high-impedance state.

2629 tbl 01

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5429FCT52CTSOB | LM140L/LM340L Series 3-Terminal Positive Regulators; Package: TO-39; No of Pins: 3; Qty per Container: 500; Container: Box |

| 5429FCT52DTD | LM140L/LM340L Series 3-Terminal Positive Regulators; Package: TO-39; No of Pins: 3; Qty per Container: 20; Container: Tray |

| 5429FCT52DTL | FAST CMOS OCTAL REGISTERED TRANSCEIVERS |

| 5429FCT52DTLB | FAST CMOS OCTAL REGISTERED TRANSCEIVERS |

| 5429FCT52DTP | LM1458/LM1558 Dual Operational Amplifier; Package: TO-99; No of Pins: 8; Qty per Container: 500; Container: Box |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5429FCT52CTSOB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:FAST CMOS OCTAL REGISTERED TRANSCEIVERS |

| 5429FCT52DTD | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:FAST CMOS OCTAL REGISTERED TRANSCEIVERS |

| 5429FCT52DTDB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:FAST CMOS OCTAL REGISTERED TRANSCEIVERS |

| 5429FCT52DTE | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:FAST CMOS OCTAL REGISTERED TRANSCEIVERS |

| 5429FCT52DTEB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:FAST CMOS OCTAL REGISTERED TRANSCEIVERS |

發(fā)布緊急采購,3分鐘左右您將得到回復。