- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67328 > 5962-8967401QX (CIRRUS LOGIC INC) 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 PDF資料下載

參數(shù)資料

| 型號: | 5962-8967401QX |

| 廠商: | CIRRUS LOGIC INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 |

| 封裝: | CERAMIC, DIP-40 |

| 文件頁數(shù): | 7/50頁 |

| 文件大?。?/td> | 520K |

| 代理商: | 5962-8967401QX |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

Also, the CS5012A/14/16’s internal RC oscillator

exhibits jitter (typically

± 0.05% of its period),

which is high compared to crystal oscillators. If

the CS5012A/14/16 is configured for synchro-

nous sampling while operating from its internal

oscillator, this jitter will directly affect sampling

purity. The user can obtain best sampling purity

while synchronously sampling by using an exter-

nal crystal-based clock.

Reset

Upon power up, the CS5012A/14/16 must be re-

set to guarantee a consistent starting condition

and initially calibrate the devices. Due to the

CS5012A/14/16’s low power dissipation and low

temperature drift, no warm-up time is required

before reset to accommodate any self-heating ef-

fects. However, the voltage reference input

should have stabilized to within 5%, 1% or

0.25% of its final value, for the CS5012A/14/16

respectively, before RST falls to guarantee an ac-

curate calibration. Later, the CS5012A/14/16 may

be reset at any time to initiate a single full cali-

bration. Reset overrides all other functions. If

reset, the CS5012A/14/16 will clear and initiate a

new calibration cycle mid-conversion or mid-

calibration.

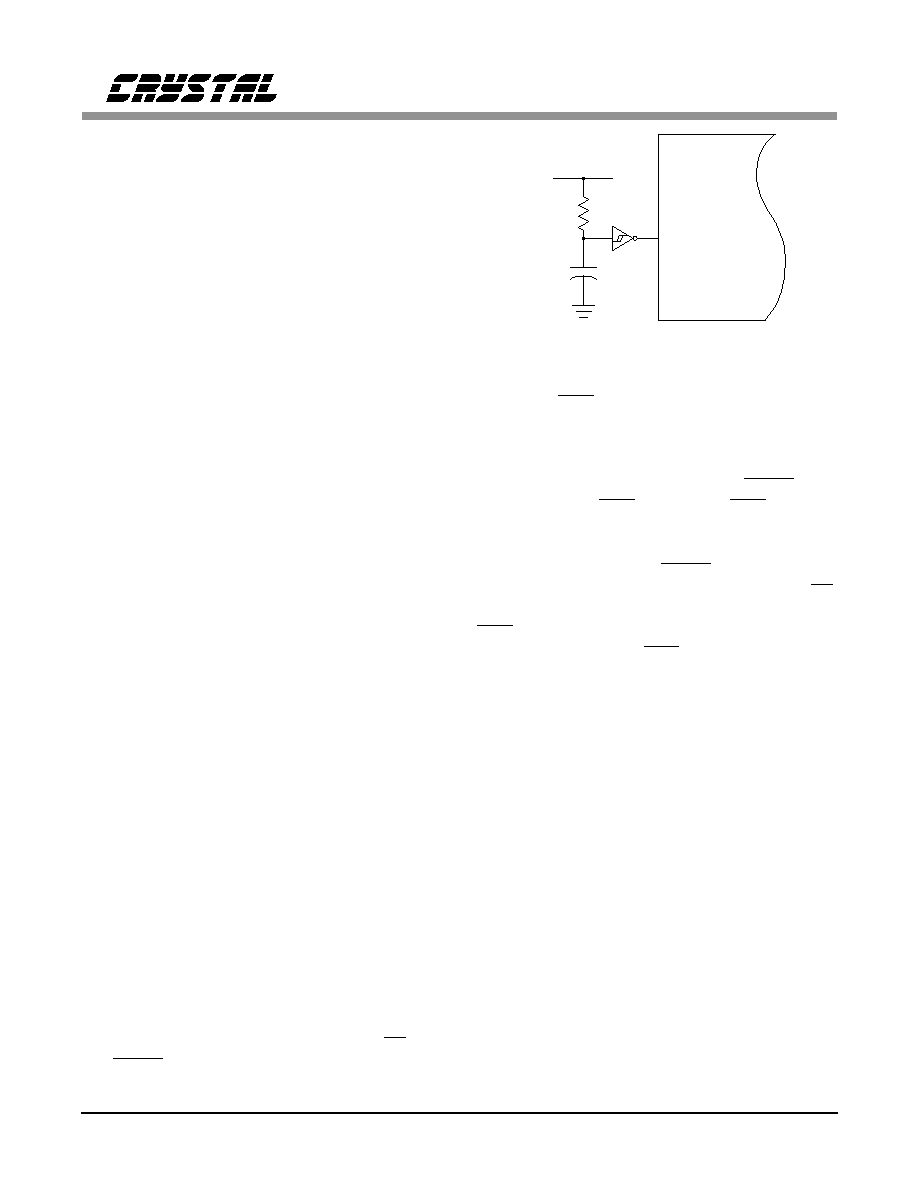

Resets can be initiated in hardware or software.

The sim p lest m ethod of resetting the

CS5012A/14/16 involves strobing the RST pin

high for at least 100 ns. When RST is brought

high all internal logic clears. When it returns low,

a full calibration begins which takes 58,280

CLKIN cycles for the CS5012A (approximately

9.1 ms with a 6.4 MHz clock) and 1,441,020

CLKIN cycles for the CS5016, CS5014 and

CS5012 (approximately 360 ms with a 4 MHz

CLKIN). A simple power-on reset circuit can be

built using a resistor and capacitor, and a

Schmitt-trigger inverter to prevent oscillation (see

Figure 6). The CS5012A/14/16 can also be reset

in software when under microprocessor control.

The CS5012A/14/16 will reset whenever CS, A0,

and HOLD are taken low simultaneously. See the

Microprocessor Interface section (below) to

eliminate the possibility of inadvertent software

reset. The EOC output remains high throughout

the calibration operation and will fall upon its

completion. It can thus be used to generate an

interrupt indicating the CS5012A/14/16 is ready

for operation. While calibrating, the HOLD input

is ignored until EOC falls. After EOC falls, six

CLKIN cycles plus 2.25

s (1.32 s for the

CS5012A -7 version only) must be allowed for

signal acquisition before HOLD is activated. Un-

der microprocessor-independent operation (CS,

RD low; A0 high) the CS5014’s and CS5016’s

EOC output will not fall at the completion of the

calibration cycle, but EOT will fall 15 CLKIN

cycles later.

Initiating Calibration

All modes of calibration can be controlled in

hardware or software. Accuracy can thereby be

insured at any time or temperature throughout

operating life. After initial calibration at power-

up, the CS5012A/14/16’s charge-redistribution

design yields better temperature drift and more

graceful aging than resistor-based technologies,

so calibration is normally only required once, af-

ter power-up.

The first mode of calibration, reset, results in a

single full calibration cycle. The second type of

calibration, "burst" cal, allows control of partial

calibration cycles.

Due to an unforeseen con-

didtion inside the part, asynchronous termination

of calibration may result in a sub-optimal result.

Burst cal should not be used.

C

R

+5V

RST

CS5012A/14/16

Figure 6. Power-on Reset Circuit

CS5012A, CS5014, CS5016

DS14F6

15

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-8967401XX | 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 5962-8967901QX | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 |

| 5962-8967602XX | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 5962-8967601XX | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 5962-8967602QX | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-8967701CA | 制造商:Linear Technology 功能描述:AMPLIFIER-OP AMP 制造商:Texas Instruments 功能描述:OP Amp Quad GP ±22V/44V 14-Pin CDIP Tube 制造商:Texas Instruments 功能描述:OP AMP QUAD GP 22V/44V 14CDIP - Rail/Tube 制造商:Texas Instruments 功能描述:LT1014AMJB QUAD PREC OP AMP |

| 5962-8967702CA | 制造商:Texas Instruments 功能描述:OP Amp Quad GP ±22V/44V 14-Pin CDIP Tube 制造商:Texas Instruments 功能描述:OP AMP QUAD GP 22V/44V 14CDIP - Rail/Tube |

| 5962-8967801XA | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| 5962-8967802XA | 制造商:Rochester Electronics LLC 功能描述:8-BIT QUAD MULT DAC IC - Bulk 制造商:Analog Devices 功能描述: |

| 5962-8967901XC | 制造商:SEI 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。